# SONY.

# CXD2565M

オーディオ用1ビット方式 DA コンバータ (DF 内蔵)

#### 概要

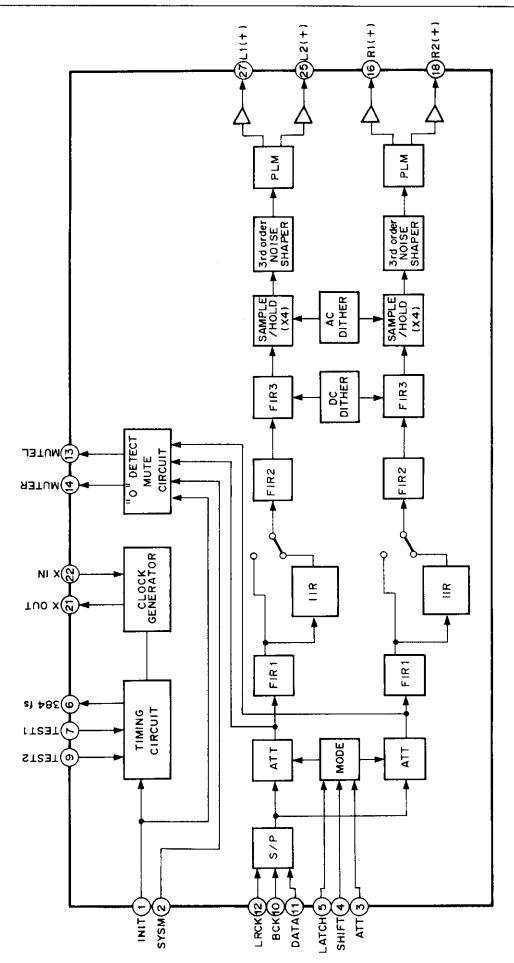

CXD2565Mは,特にCDプレーヤ用として開発された8倍 オーバーサンプリング・デジタルフィルタ内蔵の1ビット方 式ステレオDAコンバータです。(マスタークロック768fs)

#### 特 性

- デジタルフィルタ部 ・リップル:0.002dB以下

- 减衰量: 75dB以上

- DAC部

- •ダイナミックレンジ:116dB(理論値)

- •S/N:96dB以上

- 歪率: 0.004%以下

#### 特 長

- ・マスタークロック 768fs

- ソニーオリジナル新方式3次ノイズシェーパー採用

- PLM 方式パルス変換出力(コンプリメンタリー PLM)

- ダイレクト・デジタルシンク

- 入力語長 18/16 ビット選択可

#### 端子配列図 (Top View)

#### 構造

シリコンゲート CMOS

#### 用 途

CDプレーヤ, CD-Iプレーヤなど

#### 絶対最大定格

| • 電源電圧 | Vdd    | - 0.5~6.5                | V  |

|--------|--------|--------------------------|----|

| •入力電圧  | VI     | $-0.3 \sim V_{DD} + 0.3$ | V  |

| • 許容損失 | Pp (Ta | = 60°C) 500              | mW |

| •保存温度  | Tstg   | - 55~150                 | °C |

#### 推奨動作条件

| • 電源電圧                      | Vdd        | 4.75~5.25     | V   |

|-----------------------------|------------|---------------|-----|

| • 動作温度                      | Та         | $-10 \sim 60$ | °C  |

| <ul> <li>OSC 周波数</li> </ul> | Fx (768fs) | 24.0~37.0     | MHz |

本資料に記載されております規格等は、改良のため予告なく変更することがありますので、ご了承ください。 また本資料によって、記載内容に関する工業所有権の実施許諾や、その他の権利に対する保証を認めたものではありません。 なお資料中に、回路例が掲載されている場合、これらは使用上の参考として、代表的な応用例を示したものですので、これら 回路の使用に起因する損害について、当社は一切責任を負いません。

端子説明

| 端子番号 | 端子記号   | I/O | 說 明                    |  |  |

|------|--------|-----|------------------------|--|--|

| 1    | INIT   | I   | 本信号の立ち上がりエッヂで再同期       |  |  |

| 2    | SYSM   | I   | システム・ミュート入力            |  |  |

| 3    | ATT    | I   | シリアル・コントロール・データ入力      |  |  |

| 4    | SHIFT  | I   | シフト・クロック入力             |  |  |

| 5    | LATCH  | I   | ラッチ・クロック入力             |  |  |

| 6    | 384fs  | 0   | 384fsクロック出力            |  |  |

| 7    | TEST1  | I   | テスト用端子 通常使用時は"L"レベルに固定 |  |  |

| 8    | DVss   |     | デジタルGND                |  |  |

| 9    | TEST2  | I   | テスト用端子 通常使用時は"L"レベルに固定 |  |  |

| 10   | BCK    | I   | BCK入力                  |  |  |

| 11   | DATA   | I   | データ入力                  |  |  |

| 12   | LRCK   | I   | LRCK入力                 |  |  |

| 13   | MUTEL  | 0   | Lch ミュートフラグ出力          |  |  |

| 14   | MUTER  | 0   | Rchミュートフラグ出力           |  |  |

| 15   | DVDD1  |     | デジタル電源                 |  |  |

| 16   | R1 (+) | 0   | Rch PLM出力1(正相)         |  |  |

| 17   | AVDDR  |     | Rch用アナログ電源             |  |  |

| 18   | R2 (+) | 0   | Rch PLM出力2(正相)         |  |  |

| 19   | AVssR  | ·   | Rch用アナログ GND           |  |  |

| 20   | XVdd   |     | マスター・クロック電源            |  |  |

| 21   | XOUT   | 0   | X'tal 発振出力端子(768fs)    |  |  |

| 22   | XIN    | I   | X'tal 発振入力端子(768fs)    |  |  |

| 23   | XVss   |     | マスター・クロック GND          |  |  |

| 24   | AVssL  |     | Lch用アナログ GND           |  |  |

| 25   | L2 (+) | 0   | Lch PLM出力2(正相)         |  |  |

| 26   | AVDDL  |     | Lch用アナログ電源             |  |  |

| 27   | L1 (+) | 0   | Lch PLM出力1 (正相)        |  |  |

| 28   | DVDD2  |     | デジタル電源                 |  |  |

#### 電気的特性

| 項       | 8                        | 記号   | 条件           | 最小値       | 標準値 | 最大値     | 単位 |

|---------|--------------------------|------|--------------|-----------|-----|---------|----|

|         | XIN                      | VIHX |              | 0.90VDD   |     |         | V  |

| "H"入力電圧 | その他                      | VIH  |              | 0.76Vdd   |     |         | V  |

|         | XIN                      | VILX |              |           |     | 0.10Vdd | V  |

| "L"入力電圧 | その他                      | Vīl  |              |           |     | 0.24Vdd | V  |

| 入力リーク電流 |                          | II   |              | - 5.0     |     | 5.0     | μA |

|         | 384fs                    | Vон  | Io = - 0.4mA | VDD - 0.5 |     |         | V  |

|         | R1, R2 (+)<br>L1, L2 (+) | Voha | Io = -12mA   | Vdd - 0.5 |     |         | v  |

| "H"出力電圧 | XOUT                     | Vohx | Io = - 1.2mA | Vdd - 0.5 |     |         | V  |

|         | MUTEL,<br>MUTER          | Vонм | Io = - 1.0mA | Vdd - 0.5 |     |         | v  |

|         | 384fs                    | Vol  | Io = 0.4mA   |           |     | 0.4     | V  |

| "L"出力電圧 | R1, R2 (+)<br>L1, L2 (+) | Vola | Io = 12mA    |           |     | 0.5     | v  |

|         | XOUT                     | Volx | Io = 1.2mA   |           |     | 0.5     | v  |

|         | MUTEL,<br>MUTER          | Volm | Io = 1.0mA   |           |     | 0.4     | v  |

| 消費電流    | • • • • • •              | ממן  |              |           | 20  | 60      | mA |

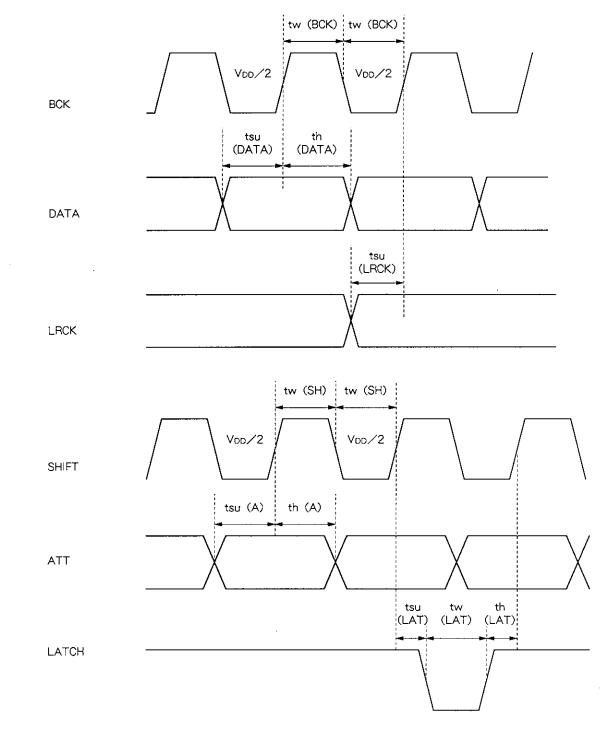

交流特性 (DVDD = XVDD = AVDDR = AVDDL = 5.0V ± 5%, DVss = XVss = AVssL = AVssR = 0V, Ta = -10~60°C)

| 項 目           | 記号         | 条件             | 最小値 | 標準値 | 最大値 | 単位   |

|---------------|------------|----------------|-----|-----|-----|------|

| BCKパルス幅       | tw (BCK)   |                | 156 |     |     | nsec |

| DATAセットアップ時間  | tsu (DATA) |                | 20  |     |     | nsec |

| DATA ホールド時間   | th (DATA)  |                | 20  |     |     | nsec |

| LRCK セットアップ時間 | tsu (LRCK) |                | 50  | -   |     | nsec |

| XIN デューティ     | duty (XIN) | VDD/2 at 33MHz |     | 50  |     | %    |

| SHIFTパルス幅     | tw (SH)    |                | 100 |     |     | nsec |

| ATTセットアップ時間   | tsu (A)    |                | 20  |     |     | nsec |

| ATT ホールド時間    | th (A)     |                | 20  |     |     | nsec |

| LATCHセットアップ時間 | tsu (LAT)  |                | 18  | 20  |     | nsec |

| LATCHホールド時間   | th (LAT)   |                | 100 |     |     | nsec |

| LATCHパルス幅     | tw (LAT)   |                | 100 |     |     | nsec |

### 入力/AC タイミング

| アナログ特性 | $(DV_{DD} = XV_{DD} = AV_{DD}R = AV_{DD}L = 5.0V, DV_{SS} = XV_{SS} = AV_{SS}L = AV_{SS}R = 0V, Ta = 25^{\circ}C)$ |

|--------|--------------------------------------------------------------------------------------------------------------------|

| ノノロノ付住 | (DVDD - AVDD - AVDDA - AVDDA - 5.0V, DVSS - AVSS - AVSSA - 0V, Ta - 25 C)                                          |

| 項目     | 記号      | 条 件                                  | 最小値 | 標準値    | 最大値    | 単位 |

|--------|---------|--------------------------------------|-----|--------|--------|----|

| 全高調波歪率 | THD + N | 入力データ 1kHz, 0dB<br>(Fs = 44.1kHz)    |     | 0.0030 | 0.0040 | %  |

| S/N比   | S∕N     | 入力データ1kHz, 0/-∞0dB<br>(Fs = 44.1kHz) | 96  |        |        | dB |

#### 機能説明

#### ① ミュート機能

- (1) ゼロ・データ検出

- 検出はアッテネーション処理の後で行われます。

- 入力データの上位14ビットがオール "0" またはオール "1" で、かつ残りの下位ビットがDCと言う状態が続いた場合、ゼロ検出フラグが出力されます。

- 検出時間は、60ミリ秒か、300ミリ秒をシリアルコントロールで選択することができます。

- ゼロ検出フラグを出力中も、デジタルフィルタは通常動作をします。

- (2) デジタル・フィルタ ミュート (D/F MUTE)

- シリアル・コントロールのATTモード中の "MUTE" が "H"の時, アクティブになります。

- D/F部からの出力は、["0" + DCオフセット] にセットされます。

- デジタルフィルタの内部演算は,通常動作をします。

- (3) ノイズ・シェーパー ミュート (NS MUTE)

- シリアル・コントロールのシステム・モード中の "NS MUTE" が "H" で以下の条件が一つでも成立した時, アク ティブになります。

- ゼロ検出フラグが立った時。

- 入力端子 "SYSM" に "H"(=ミュート)が入力された時。

- D/F MUTEフラグが立った時。

- ノイズ・シェーパーの出力は, D/F部で加算されている DC オフセット成分を持つ出力に, 切り替えられます。

- ノイズ・シェーパーの内部演算はそのまま動作させ、ミュート解除後は直ちにノイズ・シェーパーからの出力に切り 替えられます。

- (4) INIT "L" のミュート

- D/F部の入力データをゼロにセットします。

- 内部RAMをクリアします。

- D/F部の出力を["0" + DCオフセット]にセットします。

(内部RAMクリア後, 内部INIT以前)

- 内部 INIT "L"後,前置ホールド部を含むノイズ・シェーパー部レジスタをクリアし,出力をデューティー 50%の PWM (0に相当)にセットします。

② ミュート・フラグ出力(MUTEL, MUTER 端子)

- 以下の条件のうち一つでも成立した時に、ミュート・アクティブのフラグをMUTEL、MUTER 端子から出力します。 (フラグの極正は、シリアル・コントロールで選択可能です)

- ゼロ検出フラグが立った時。

- 入力端子 "SYSM" に "H" (=ミュート) が入力された時。

- D/F MUTEフラグが立った時。

- 外部 INIT がアクティブになった時。

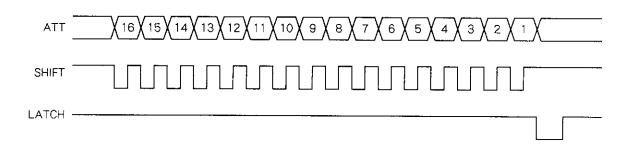

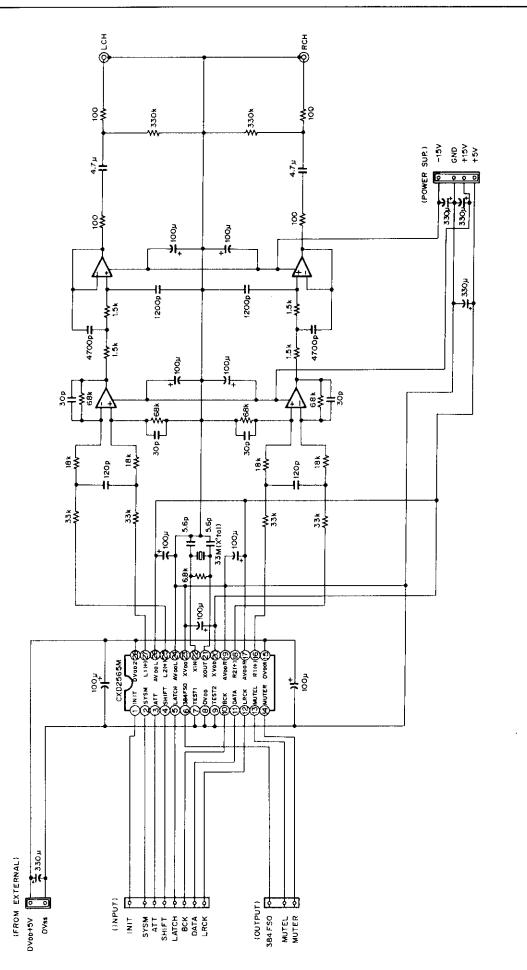

③ シリアル・コントロール

- ATT, SHIFT, LATCH端子に、モードデータを転送することによりモード設定を行います。

- 転送フォーマットを以下に示します。

- ビット1のデータは常に"O"とします。

- ビット2のデータが "0"の時アッテネートモードとなります。

ビット2のデータが "1"の時システムモードとなります。

- 設定は、外部 INIT 解除後に行います。

(次頁にモード設定表を示します)

- \* SYNC機能について

- シリアル・コントロールのシステムモードの中の "SYNC" が "H" にセットされる時, その立ち上がり時より一回だけ, 再同期をかけにいきます。

- 内部の同期がとれるまで,最低4fs周期,最高5fs周期を要します。

シリアル・コントロール

• アッテネート・モード

| ビット | モード・フラグ | 機能              | "H"     | "L"       |

|-----|---------|-----------------|---------|-----------|

| 1   | MODE1   | MODE 切り替え       | テストモード  | ノーマルモード   |

| 2   | MODE2   | MODE 切り替え       | システムモード | アッテネートモード |

| 3   | EMP     | ディエンファシス        | ON      | OFF       |

| 4   | MUTE    | "0" + DCオフセット出力 | ON      | OFF       |

| 5   | ATT1    | アッテネートデータ (MSB) |         |           |

| 6   | ATT2    | アッテネートデータ       |         |           |

| 7   | ATT3    | アッテネートデータ       |         |           |

| 8   | ATT4    | アッテネートデータ       |         |           |

| 9   | ATT5    | アッテネートデータ       |         |           |

| 10  | ATT6    | アッテネートデータ       |         |           |

| 11  | ATT7    | アッテネートデータ       |         |           |

| 12  | ATT8    | アッテネートデータ       |         |           |

| 13  | ATT9    | アッテネートデータ       |         |           |

| 14  | ATT10   | アッテネートデータ       |         |           |

| 15  | ATT11   | アッテネートデータ       |         |           |

| 16  | ATT12   | アッテネートデータ (LSB) |         |           |

\* INIT "L" で, MODE1, MODE2, EMP, MUTEは "L" にリセット, ATTは "400"Hにセット

#### • システム・モード

| ビット | モード・フラグ | 機能              | "H"      | "L"       |

|-----|---------|-----------------|----------|-----------|

| 1   | MODE1   | MODE 切り替え       | テストモード   | ノーマルモード   |

| 2   | MODE2   | MODE切り替え        | システムモード  | アッテネートモード |

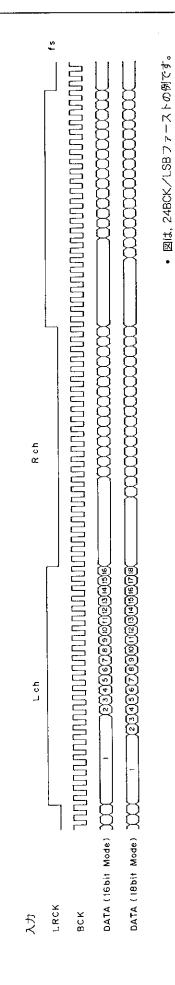

| 3   | IFORM   | 入力データ形式         | LSBファースト | MSBファースト  |

| 4   | IBIT    | 入力データ語長         | 18ビット    | 16ビット     |

| 5   |         |                 | don't    | care      |

| 6   |         |                 | don't    | care      |

| 7   |         |                 | don't    | care      |

| 8   | TEST1   | テストモードの設定       | 通常使用時は   | t"L"に固定   |

| 9   | TEST2   | テストモードの設定       | 通常使用時は   | t"L"に固定   |

| 10  | NS      | ノイズシェーピング       | don't    | care      |

| 11  | MT1     | ゼロデータ検出時間       | 60ミリ秒    | 300ミリ秒    |

| 12  | MT2     | ゼロミュートフラグの極性    | "H"でミュート | "L" でミュート |

| 13  | FS32    | ディエンファシスの fsの選択 | * 下ā     | 表参照       |

| 14  | FS48    | ディエンファシスのfsの選択  | * 下書     | 表参照       |

| 15  | SYNC    | 入出力の同期          | ON       | OFF       |

| 16  | NSMUTE  | NSミュート機能        | ON       | OFF       |

\* INIT "L" で, すべて "L" にリセット

\* ディエンファシスのfsの選択

|    |      | 32.0k | 44.1k | 48.0k | 37.8k |

|----|------|-------|-------|-------|-------|

| 13 | FS32 | "H"   | "L"   | "L"   | "H"   |

| 14 | FS48 | "H"   | "L"   | "H"   | "L"   |

- ④ INIT 機能

- 外部 INIT 信号立ち上がり後, 再同期がかけられたら直ちに D/F部と NS部は同時にリセット解除されます。

- 外部LRCK は外部 INIT 信号によって変化しないので, 外部 INIT 信号の立ち上がり後, 最初の外部LRCK に対し, 内部 LRCK の位相をマスタークロック・レベルで合わせ込みます。

- 内部の同期がとれるまで最低4fs周期,最高5fs周期を要します。

- 内部 INIT は,外部 INIT 信号立ち下がり後,約2~2.5 ミリ秒遅らせています。

⑤ 倍速の動作について

- 倍速で入力してきた信号に対して同期を保ち、内部演算は標準速のままで行われます。

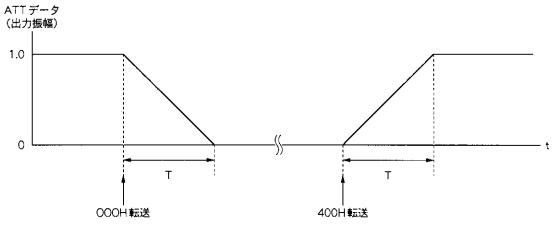

- ⑥ アッテネータ

- ATT データはビット5 (MSB) ~ビット16 (LSB) の12ビットを使って転送されます。大きさは、000H (0.0) ~400H

(1.0) となっています。

INIT: "L"でATTデータとして400Hがセットされます。

ソフトミューティングはATTとして000Hを転送することにより行います。解除するときは、ソフトミューティングをかけ る前のATTデータ(上図では400H)を転送します。

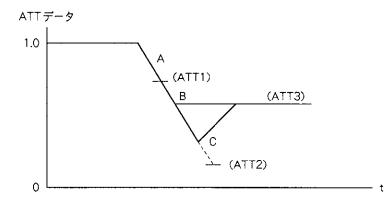

このように新しい ATT データへは、常にソフトミューティングの動作で移っていきます。上図のように ATT1 > ATT3 > ATT2 という ATT データを考え、まず ATT1 が転送され次に ATT2 が転送されたとします。ATT1 の値になる前に(図中 A の状態)ATT2 が転送された場合は ATT1 は無視されそのまま ATT2 の値に近づいていきます。

次にATT2が転送され、ATT2の値になる前に(図中BまたはC)ATT3が転送されると、ATT2は無視され、ATT3の値に近づいていきます。

データ入力タイミング

- 12 -

CXD2565M

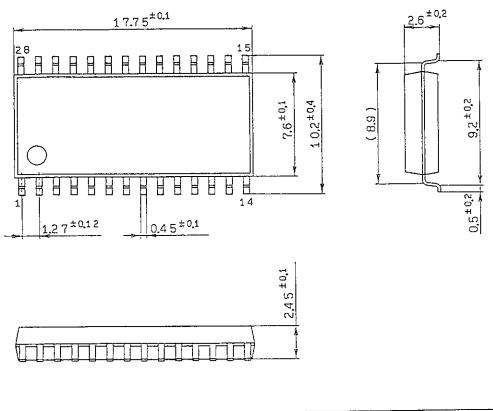

外形寸法図 単位:mm

28pin SOP (Plastic) 375mil

| SONY  | NAME | SOP-28P-L121      |

|-------|------|-------------------|

| EIAJ  | NAME | *SOP028-P-0300-AX |

| JEDEC | CODE |                   |