# Service Manual

**SERVICE GUIDE**

ORDER NO. RRV1710

DVD PLAYER DVD PLAYER

DVL-90 DVL-700

### **CONTENTS**

| 1. DISASSEMBLY 2                      | 3. ELECTRICAL DESCRIPTION            | 12 |

|---------------------------------------|--------------------------------------|----|

| 1.1 DV-500 2                          | 3.1 DV-500                           | 12 |

| 1.2 DVL-90 AND DVL-700 4              | 3.2 DVL-90 AND DVL-700               | 20 |

| 2. MECHANISM DESCRIPTION 8            | 4. TEST MODE                         | 24 |

| 2.1 NEW MECHANISM 8                   | 4.1 HOW TO ENTER/EXIT                |    |

| 2.2 MECHANISM OF DVL-90 AND DVL-700 9 | FROM TEST MODE                       | 24 |

|                                       | 4.2 TEST MODE OPERATIONS             | 24 |

|                                       | 4.3 NOTES                            | 25 |

|                                       | 4.4 TEST MODE DISPLAY SPECIFICATIONS | 25 |

|                                       | 5. IC INFORMATION                    | 27 |

# 1. DISASSEMBLY

# 1.1 DV-500

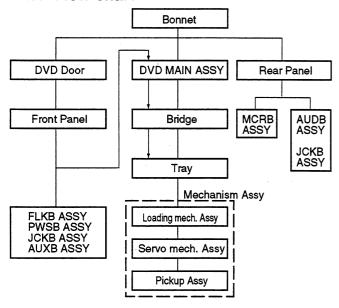

#### 1.1.1 Flow chart

Note: For details, Refer to "7.2 DISASSEMBLY/ASSEMBLY" in the service manual RRV1708 for DV-500.

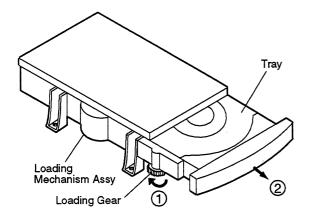

# 1.1.2 Manual Setting of the Tray Unit to Its Open Position

Fig. 1-1

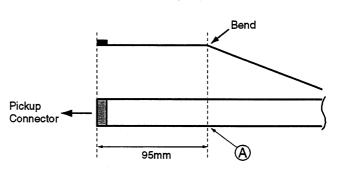

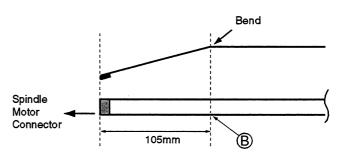

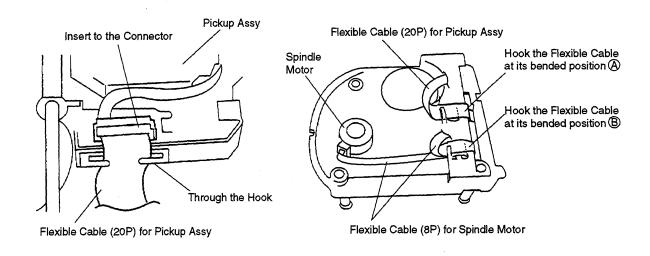

# 1.1.3 Style the Flexible Cable for Spindle Motor and Pickup

(1) Bend the Pickup Flexible Cable (20P)

(2) Bend the Spindle Motor Flexible Cable (8P)

Fig. 1-2-1

Fig. 1-2-2

# 1.1.4 Style the Flexible Cable

Fig. 1-3

#### 1.2 DVL-90 and DVL-700

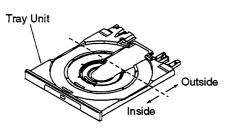

# 1.2.1 Manual Setting of the Tray Unit to Its **Open Position**

(1) Make sure that the Carriage Assy lens stops at a position outside the broken line indicated in Fig. 1-4.

Fig. 1-4

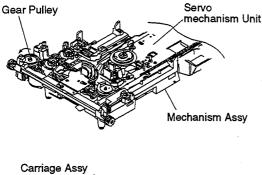

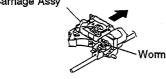

(2) If the lens remains in a position inside the broken line in Fig. 1-4, locate the lens in a position outside the broken line in the following manner: Insert your hand from the lower-left side of the Tray Unit, and turn the Gear Pulley of the Loading Mechanism Unit counterclockwise until it stops so that the Servo Mechanism rises. Then slowly turn the Worm of the Carriage Assy counterclockwise so that the Carriage Assy moves backward and the Carriage Assy lens moves to a position outside the broken line in Fig. 1-4. (Without this procedure, the unit will be in CD Tray Open mode.)

Fig. 1-5

(3) Turn the Gear Pulley of the Loading Mechanism Unit clockwise. When the Servo Mechanism Unit goes down and the Tray Unit moves forward, pull the Tray Unit slowly by hand to its open position.

Note: For removal of the main parts, Refer to "7.2 DISASSEMBLY/ASSEMBLY" in the service manual RRV1709 for DVL-90 and DVL-700.

#### 1.2.2 Removal of Mechanism Parts

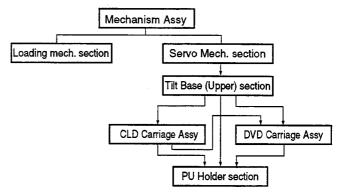

#### Flowchart of Mechanism Assy Removal

#### Removal of the Mechanism Assy

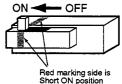

- (1) Press the LD OPEN key to remove the Tray Unit. (The Carriage moves to the LD side.) Short SW

- (2) Disconnect the AC Power Cord.

- (3) Set the short-circuit switch of the DVD Carriage Assy so that the position pointer is aligned with the mark (Short-Circuit mode.)

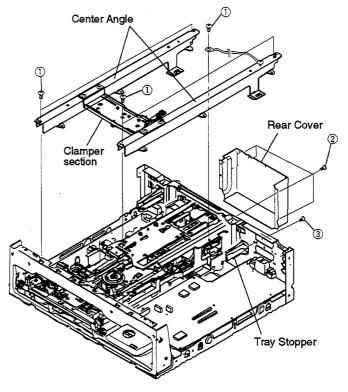

- (4) Remove the Clamper section. (1) 5 screws)

- (5) Remove the Rear Cover. (2) 4 screws)

- (6) Remove the Tray Stopper that holds the Flexible Cable. (3) 1 screw)

Fig. 1-6

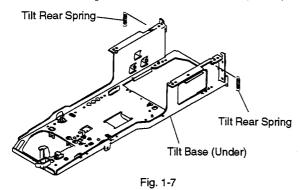

(7) Remove the two Tilt Rear Springs located at the Rear Panel side of the Servo Mechanism section, and hook them onto the provisional hooks Tilt Base (Under).

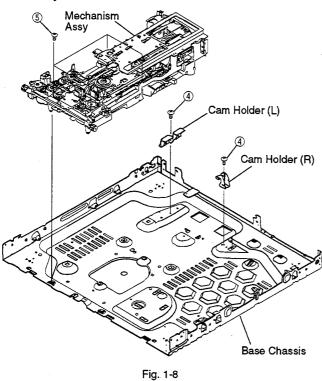

- (8) Remove the Cam Holder (L) and Cam Holder (R) located on each side of the Mechanism Assy. (4) 2 screws)

- (9) Remove the four mounting screws ⑤ of the Mechanism Assy.

- (10) Disconnect the three Flexible Cables connecting the Mechanism Assy and CLD MAIN Assy from CLD MAIN Assy, one Flexible Cable connecting the Mechanism Assy and DVD MAIN Assy from the DVD MAIN Assy, and the Connector Assy (2P) connecting the Mechanism Assy and the POWER SUPPLY Assy from the POWER SUPPLY Assy.

- (11) Slide the Mechanism Assy backward while raising it lightly until its front moves to a position where it can be pulled out of the Panel Holder. Then raise the front of the Mechanism Assy and pull it diagonally upward out through the Rear Panel.

#### Removal of the Servo Mechanism Section

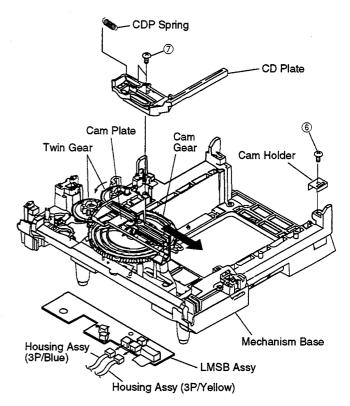

- (1) Remove the Housing Assy (3P/yellow) for FG and the Housing Assy for detection of carriage position (3P/blue) from the LMSB Assy.

- (2) Remove the Cam Holder. (6) 1 screw)

- (3) Remove the CD Plate and the CDP Spring. (7) 2 screws)

- (4) While pressing the Cam Plate toward the inside (right), turn the Twin Gear counterclockwise until it stops (the Twin Gear and the Cam Gear will become disengaged.)

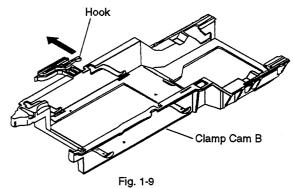

- (5) Bend the hook of Clamp Cam B in the direction indicated by the arrow until it stops.

- (6) Remove the Servo Mechanism Unit from the Clamp Cam by raising it directly upward.

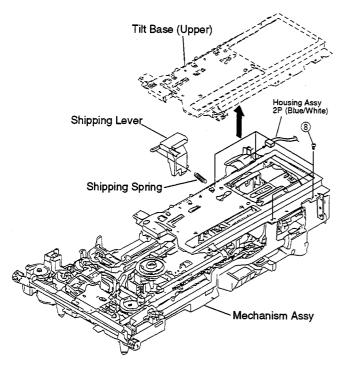

#### Removal of the Tilt Base (Upper)

- (1) Remove the Shipping Spring and Shipping Lever.

- (2) Remove the Housing Assy 2P (blue/white) from the TNMB Assy.

- (3) Remove the Tilt Base (Upper). (8 4 screws)

Fig. 1-10

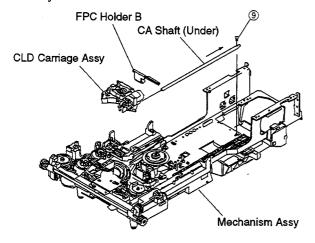

### • Removal of the CLD Carriage Assy

- (1) Remove FPC Holder B and disconnect the PU flexible cable.

- (2) Remove the fixing screw (9) of the CA Shaft (Under) and remove it from the CLD Carriage Assy.

- (3) Remove the CLD Carriage Assy from the Mechanism Assy.

Fig. 1-11

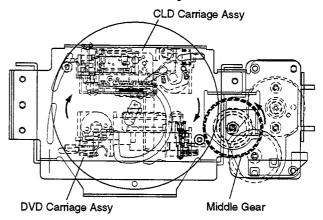

#### Removal of the DVD Carriage Assy

(1) Turn the PU Holder 180 degrees by turning the Middle Gear of the Carriage Change Mechanism counterclockwise until it stops.

Fig. 1-12 Mechanism Assy (Rear View)

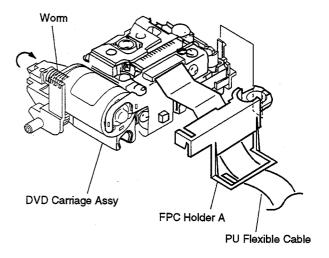

- (2) Move the DVD Carriage Assy forward by turning its Worm clockwise, and remove the DVD Carriage Assy.

- (3) Remove FPC Holder A and disconnect the PU flexible cable.

Fig. 1-13

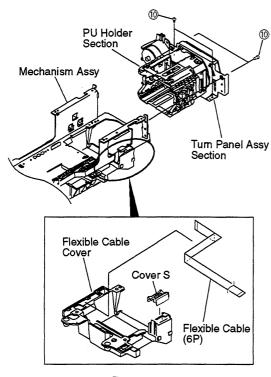

#### • Removal of the PU Holder Section

- (1) Place the two Carriage Assys in the PU Holder section.

- (2) Disconnect the Flexible Cable from the TNMB Assy.

- (3) Remove the four fixing screws @ from the Turn Panel Assy.

- (4) Remove the Cover S and disconnect the Flexible Cable from the Flexible Cable Cover.

Fig. 1-14

#### 1.2.3 Style the Flexible Cable

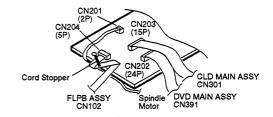

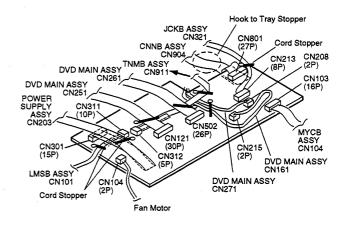

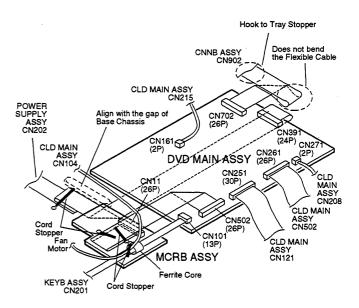

#### • POWER SUPPLY ASSY

#### • CLD MAIN ASSY

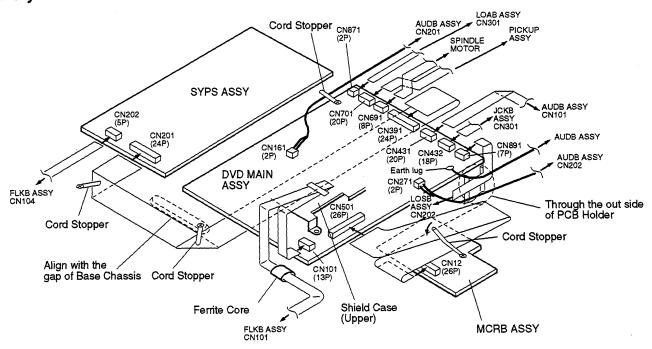

• DVD MAIN ASSY, MCRB ASSY

Fig. 1-15

# 2. MECHANISM DESCRIPTION

#### 2.1 NEW MECHANISM

#### (1) Skew Margin

The skew margin allowed for the DVD system is about half that allowed for the CD system, and the parallelism (between the optical pickup lens and the disc) required for the optical pickup drive is also critical. To secure the parallelism between the spindle motor fixing face and the guide bar fixing face for the optical pickup, 1.6-ton-rated sheet metal is used. achieving deviation in parallelism around half of that in the conventional CD specifications. In addition, use of sheet metal has enabled stable playback free of degradation caused by temperature changes, transportation and so on. However, this is not sufficient for the specifications required for the DVD system, so a newly developed tilting adjustment mechanism is also added. As for optical pickups for conventional CDs, titling adjustment against the drive is performed by the tilting adjustment mechanism of the actuator. For the optical pickup of the DVD system, a newly developed mechanism that adjusts the tilting of the entire optical pickup mechanism against the drive is used, which has resulted in a great improvement in parallelism and enable stable playback without a tilt servo mechanism. For the DVL-90 and DVL-700, a full use of the tilt servo mechanism, which is essential for playback of an LD, has yielded stable playback of DVDs.

#### (2) Disc Centering

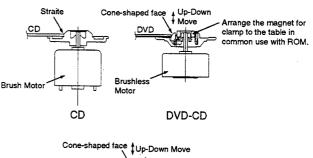

Conventional CD players perform disc centering with a straight cylinder, detecting the inner periphery of a disc. Centering of a DVD must be done by the disc edge, because DVDs have a multilayered structure. For the DV-500, a mechanism that perpendicularly moves a cone-shaped centering hub and that has been used in conventional LD players is added for DVD centering. For the DVL-90 and DVL-700, this mechanism is already provided and can be also used for DVD centering.

#### (3) Spindle Motor

For DVD playback, a spindle motor for CD-ROMs and not for conventional CDs is required, because the rotation speed for a DVD is equivalent of four times that for CD-ROM. In addition, a brushless high-torque motor is used to secure full reliability as increases in axial looseness of the motor caused by a long use would induce inclination of the motor against the optical pickup, which would cause trouble in playback. For the DVL-90 and DVL-700, a spindle motor for conventional LDs is used.

Fig. 2-1 Spindle Motor and Disc Centering

#### (4) Optical Pickup Positioning Mechanism

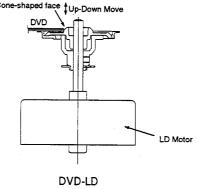

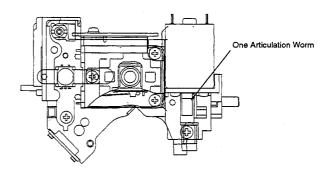

A high-speed search mechanism is essential for seamless playback such as multistory and multiangle playback. For the DV-500, a high-speed search mechanism used for CD-ROMs is used, with a backlashless high-speed gear mechanism used in quadruple-speed CD-ROMs, but with modifications for use with the DV-500 servo circuits.

Variable specifications required for DVD and CD-ROM (stable sequential playback for DVD and random-access response speed for CD-ROM) can be achieved only by changing the combination of gears in the same chassis, without changing the pitch between the motor and the guide shaft. The optical pickup positioning mechanism for the DVL-90 and DVL-700 greatly differs from that for the DV-500.

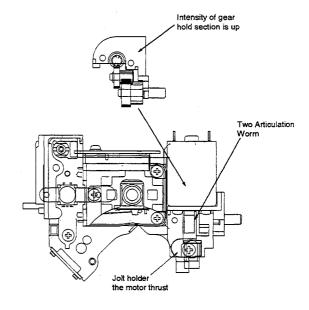

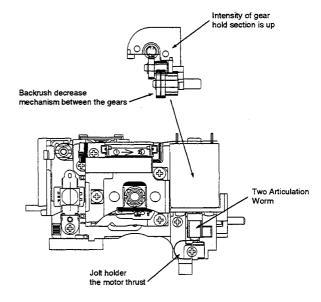

Fig. 2-2 Positioning Mechanism

#### 2.2 MECHANISM OF DVL-90 AND DVL-700

#### (1) Optical Pickup Structure

One pickup for DVD playback and another pickup for playback of LDs and CDs are provided to perform one-side playback of DVDs, both-side playback of LDs, and playback of CDs.

The optical pickup used for LD playback is of proven quality. The optical pickup used for DVD playback is a dedicated one, which is equipped with an optical system required for DVD playback such as a high-NA-glass pressed lens and a short-wave length laser, as well as a motor mechanism for self-advancing, and a tilt sensor.

#### (2) Tray Unit Structure

Two types of trays equipped with LD players as standard specification are provided: a tray for 12cm discs and a tray for 30cm discs.

A common carriage mechanism for LD player is shared between both trays.

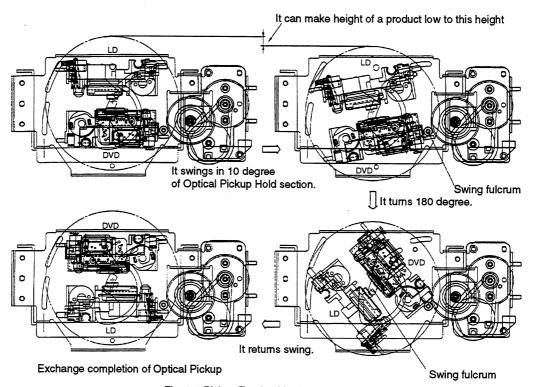

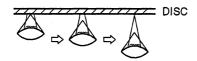

#### (3) Optical Pickup Changing Mechanism

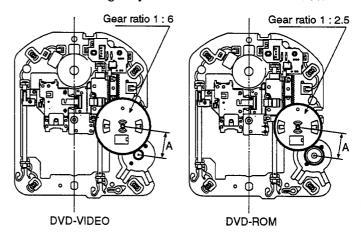

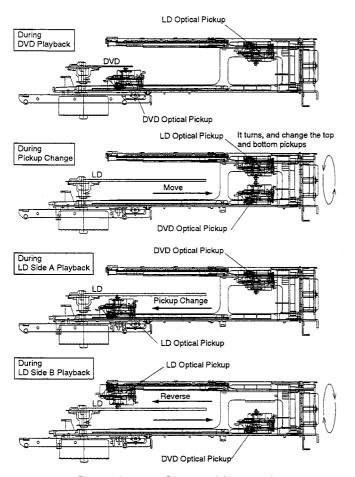

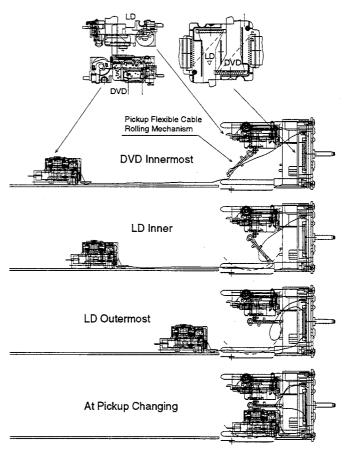

One of the optical pickups is placed in the playback position according to the tray used, and another optical pickup is waiting at the rear of the Optical Pickup Positioning Mechanism. This waiting portion is a rolling mechanism that can house both optical pickups at the same time symmetrically at the upper and lower positions. When the optical pickup at the playback position is not the one for the type of disc to be played, this pickup is retracted to the Rolling Mechanism, and both optical pickups are rotated together by 180 degrees. Then, another optical pickup is moved to the playback position. For playback of side B of an LD, the optical pickup for LDs is rotated to side-B position, thus enabling seamless playback of both sides of an LD. Both optical pickups share the same guide bars, one provided for side A and the other for side B. For tracking of DVD playback, a one-beam tracking system is adopted. The Rolling Mechanism rotates with both pickups retracted. To reduce the rotation radius, a rotational fulcrum is separately provided, and the two pickups are together swung about 10 degrees and then rotated. For the Rolling Mechanism Drive, a dedicated motor is used for speedup of changing. At the same time, a motor drive that can function at twice the speed of conventional LD drives is provided for each pickup. In addition, a Tilt Servo Mechanism, which is essential for playback of LDs, is provided. This Tilt Servo Mechanism also enables stable playback of DVDs.

All these provisions for the Optical Pickup Positioning Mechanism add weight to the mechanism. Therefore, a Clamp Mechanism interlocked with the Tray Carriage Mechanism is newly employed for the protection of the Positioning Mechanism during disc removal and transportation.

Optical Pickup for Current LD

Optical Pickup for New LD

Optical Pickup for New DVD

Fig. 2-3 Optical Pickup Structures

#### (4) Optical Pickup-Positioning Mechanism

The feed rate of the self-advancing motor drives provided for the two optical pickups is twice that for conventional motor drives for LDs, because the feed rate for conventional motor drives for LDs is not sufficient for seamless playback. Associated with the speedup of the motor drive are an enhancement of the Gear Hold Section and a motor Thrust Adjuster. For the optical pickup for DVDs, a device to reduce backlash between gears is also provided.

Fig. 2-4 Summary Diagram of Chang and Reverse the Pickup

Fig. 2-5 Flexible Cable Store simulation during Pickup move

Fig. 2-6 Pickup Turning Mechanism Structure

# 3. ELECTRICAL DESCRIPTION

# 3.1 DV-500

# 3.1.1 OVERALL BLOCK DIAGRAM

#### 3.1.2 OPERATIONS

#### (1) P-ON

When the P-ON command is sent from a button on the remote control unit or on the main unit, the FL control computer (PD4753B) responds to the command. First, pin 21 (POWER ON) is set to H so that 5 V and 3.3 V of the SYPS Assy and 8 V of the DVD MAIN Assy are on. Then, pin 22 (XRES) is set to H so that each IC is released from reset status and initialized.

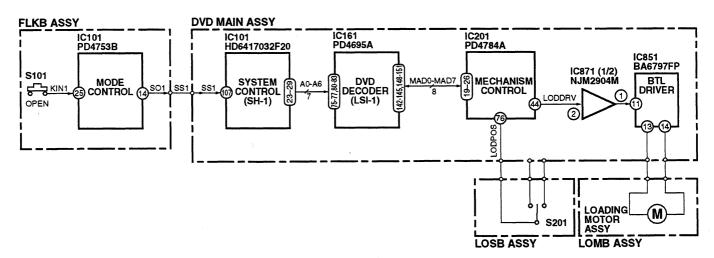

#### (2) Loading

When the FL control computer (PD4753B) recognizes the OPEN command, it transfers the corresponding data serially to the system control computer (SH-1.) When receiving the data, SH-1 translates the mode and writes the corresponding operation command to the data memory of LSI-1 through an address bus. This operation command is transferred to the mechanism control computer (PD4784A) through an address data bus. (Other operation commands such as PLAY and

SEARCH are also transferred from SH-1 to the mechanism control computer through LSI-1 in the same way.)

Once receiving the command, the mechanism control computer controls the loading motor via pin 44 (LOAD DRV) while monitoring pin 76 (LOAD POS) in the following manner: the PWM output from pin 44 goes through the OPAMP (IC871) and controls the motor with the Motor Driver BA6797FP (IC851.) Thus, the disc is set into the main unit.

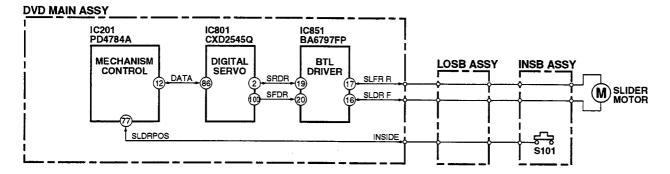

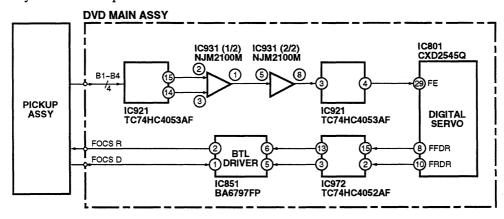

# (3) Slider Movement into the Minimum Internal Circumference

When a disc is loaded, the mechanism control computer orders the pickup to move to the minimum internal circumference, which is the disc-sensing position, while monitoring pin 77 (SLDR POS.) This movement to the minimum internal circumference is performed by the mechanism control

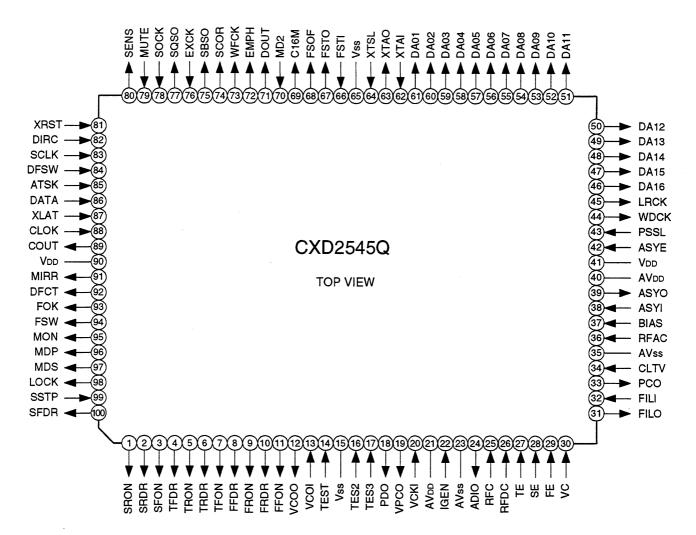

computer, which sends serial data to Digital Servo IC CXD2545Q (IC801). CXD2545Q, corresponding to the Slider Drive command, outputs the PWM signal from pin 2 and pin 100 (SLDR DRV), and through the Motor Driver, causes the Slider Motor to move.

#### (4) Disc Sensing

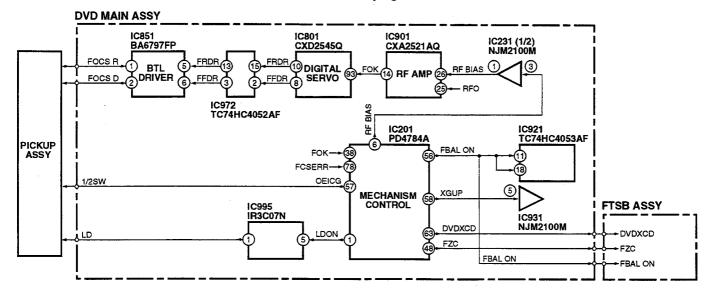

At the next step, disc sensing is performed by the mechanism control computer. As the initial setting, the following settings are made: Pin 57 (OEIC GAIN) = L; pin 58 (XGAIN UP) = H; pin 56 (FBAL ON) = L; pin 48 (DVD/XCD) = H. Then pin 1 (LD ON) is set to H so that the LD Driver IR3C07 (IC995) is activated to light LD ON. Then the lens is moved to its highest position in response to the FCS DRV signal from pins 8 and 10 of CXD2545Q. The above actions are all ordered by the mechanism control computer. At this stage, pin 6 (RF BLAS) of the mechanism computer outputs the offset correction to cancel offset of RFO (IC901 pin 25.).

The lens then moves down at a constant speed, and the disc sensing starts when the following conditions are satisfied: Pin 63 (FZC) of the mechanism control computer = L and pin 38 (FOK) = H. Disc sensing is conducted using the sinewave signal from pin 78 (FCS ERR) of the mechanism control computer. As the level of the reflected light differs depending on the disc to be played back, to obtain the optimum level, after the first sweep, OEIC GAIN is set to H and after the second sweep, XGAIN UP is set to L. Sweep is conducted a maximum of three times. If the conditions FZC = L and FOK = H are not satisfied after the third sweep, the status is judged as NO DISC.

#### (5) Disc-Size Sensing (8 cm/12 cm)

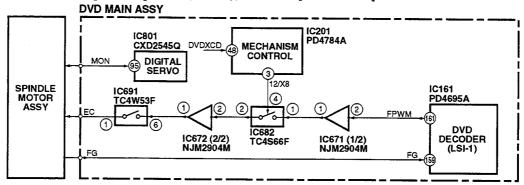

After disc sensing, disc-size sensing is performed. The disc size is sensed by rotating and accelerating the spindle motor and by calculating its rotation speed and time as follows: First, the Motor-On command is transmitted to CXD2545Q, which sets pin 95 (MON) to H and activates the drive circuit of the spindle motor; At the same time, the Acceleration command is transmitted to LSI-1, and the PWM signal for the FG servo for maximum acceleration is output from pin 161 (FPWM);

The FPWM signal, passing via IC671 and IC672, orders acceleration at the motor; To obtain data on the motor's rotation speed, the mechanism control computer reads the FG pulse, which is output from the motor and input to pin 159 (FG) of LSI-1.

Thus, disc-size sensing is completed, and the setting of pin 3 (8/X12) and pin 48 (DVD/XCD) of the mechanism control computer are completed

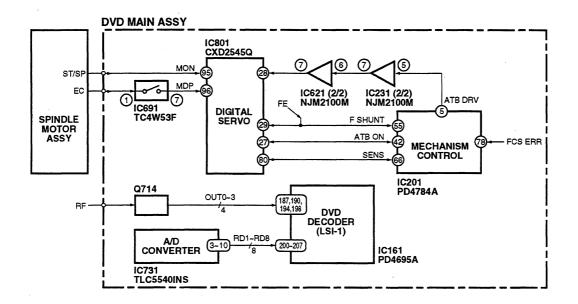

#### (6) CD Focus-In

First, the spindle motor is rotated, and the disc is turned. To do this, unlike the case of disc sensing, CXD2545Q is used, because the analog switch of IC691 has been set to the side of pin 7 in response to the DVD/XCD signal. Pin 95 (MON) of CXD2545Q is set to H to activate the motor, and the SPDL ERR signal is output from pin 96 (MDP.) The MDP is at first accelerated in Kick mode up to 600 rpm. If the rotation speed exceeds 600 rpm, the mechanism control computer sets the unit to STOP mode and switches the MDP to HI-ZI, which puts the motor in Free-Run mode. The lens moves to the lowest position after LD ON because the drive direction of the FCS is reversed by IC972. Then, the mechanism control computer sets pin 55 (F SHUNT) to H and shunts the FCS ERR signal on the way to CXD2545Q by O946. This is to prevent focusing in with noise before a real sinewave signal or pseudo-sinewave signal. Then the mechanism control computer sends the Auto-Focus command to CXD2545O. The lens moves up at constant speed. The mechanism control computer, which monitors pin 78 (FCS ERR) at the same time, sets pin 55 (F SHUNT) to L when the peak of a sinewave signal exceeds the threshold value that was set upon disc sensing. FCS LOOP is set to ON if the following two conditions are met: the FE of the trailing edge of the sinewave signal crosses the zero point, and pin 93 (FOK) of CXD2545O is set to H.

#### (7) CD Startup

The mechanism control computer recognizes FCS ON by monitoring pin 80 (SENS) of CXD2545Q and orders the pickup to move to the outer periphery by a certain distance. Then, it starts Auto Tracking Balance (ATB). In performing ATB, pin 42 (ATB ON) is set to H, and the LPF SW (Q811) of the TE is set to ON, which sets the DC offset value of the TE written as a register value inside CXD2545Q and corrects the offset value to become 0 with pin 5 (ATB DRV). Then AGC is performed. FCS and TRKG are conducted by CXD2545Q. The RF level is controlled so that the level of the RF signal, which is converted from analog to digital at IC 731 and then input via pins 200-207 of LSI-1, is kept constant by controlling the RF amplifier gain of Q714 variably with OUT 0-OUT 3. Then TOC Read and PLAY are performed.

#### (8) DVD Focus-In

Most of the DVD Focus-In operations are the same as those for a CD, except for following two points:

- (1) The sweep direction for focusing is reversed; i.e. the sweep direction is the same as that for disc sensing.

- (2) the spindle motor is not rotated for focusing.

#### (9) DVD Startup

DVD startup operations are mostly the same as those for a CD, except the following: The rotation of the spindle motor is performed after FCS ON, ATB and AGC are conducted without moving the pickup, and NAVI Information Reading and PLAY are then performed.

#### (10) Focus Loop

The photodetector signal is divided into signals B1, B2, B3, B4, which are output by the OEIC of the pickup and sent through the Focus Balance switch of IC921 and converted into the FCS ERR signal at the FE AMP of IC931. This FCS ERR signal is then input via pin 29 of the Digital Servo IC (CXD2545Q), where the signal is internally processed, and the FCS DRV signal is output from Pins 8 and 10, and the Focus Servo is driven by the Driver Amplifier of IC851.

#### (11) Slider Loop

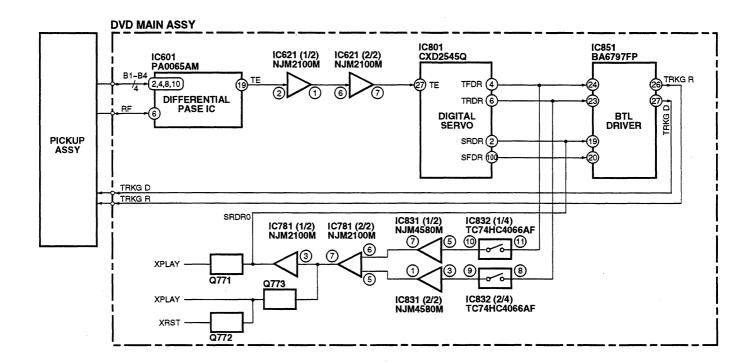

The Slider Error signal is output from pins 4 and 6 (TRK DRV output) of Digital Servo IC. The Slider Error signal, which goes through the Slider Error Amplifier (IC781) is mixed with the signal from pins 2 and 100 (slider control output) of the Digital Servo IC at the Driver Amplifier (IC851) and drives the slider. Q771 and Q773 are loop switches.

#### (12) Tracking Loop

The TE signal is formed when the B1, B2, B3, B4 signals output from OEIC of the pickup and the RF signal are input to the Time-Difference-TE-Forming IC (IC601.) The TE signal, output from pin 19, to which the offset signal is added in IC231, is then input via pin 27 of Digital Servo IC (CXD2545Q). The signal is then digitally processed, and the Kick Brake Pulse is switched, and the TRKG DRV signal is output from pins 4 and 6. The Tracking Servo is then driven by the Driver Amplifier (IC851.)

# DV-500, DVL-90, DVL-700

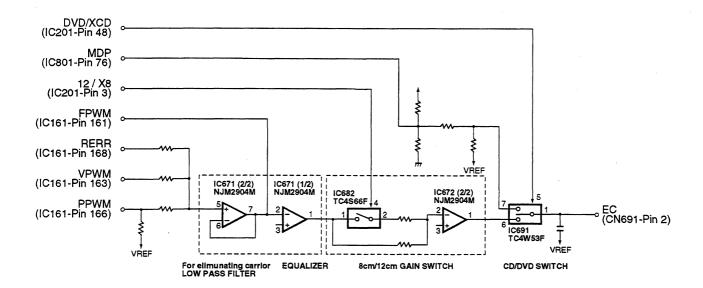

#### (13) Spindle Servo Block

| IC161             | FPWM<br>(Pin 161) | RERR<br>(Pin 168) | VPWM<br>(Pin 163) | PPWM<br>(Pin 166) |

|-------------------|-------------------|-------------------|-------------------|-------------------|

| at Stop           | duty 50%          | Z                 | Z                 | Z                 |

| at Acceleration   | duty 99%          | Z                 | Z                 | Z                 |

| at Lock           | Z                 | Z                 | about<br>50%      | about<br>38%      |

| at Deceleation    | duty 0%           | Z                 | Z                 | Z                 |

| Carrier Frequency | 55kHz             | <u> </u>          | 104kHz            | 167kHz            |

"Z": High Impedance

In actual usage, rough servo status caused by the RERR signal is very short, and few cases can be identified clearly.

For a setting sake, rough servo is a transitional status from the FG servo to the Speed/Phase servo. As for gain switching for 8 cm/12 cm, the gain is decreased for an 8-cm disc by increasing the input resistance of the IC672 Operation Amplifier. Conversely, the gain is increased for a 12-cm disc by parallel connection of the input resistance.

Switching between a CD and DVD is done by IC691 with the MDP output and the DVD/XCD output for CDs from CXD2545Q.

The FG pulse is output from the open collector of the motor only if pin 95 (MON) of IC801 (CXD2545Q) is set to "H." The FG pulse pulled up with R699 4.7 k $\Omega$  is input to pin 159 of IC161(LSI-1.)

The number of FG pulsed is 6 per rotation.

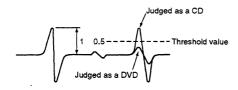

#### (14) Basic Method for Disc Sensing

#### • Disc sensing

① Lens sweep  $Up \rightarrow Down$

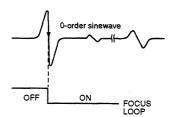

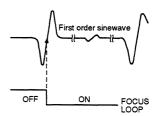

② FOCS sinewave output signal Judged by the ratio of <u>first-order sinewave</u> to 0-order sinewave

<0.5 : Judged as a DVD ≥0.5 : Judged as a CD

Note: The pseudo-sinewave signal is not blinded.

#### • Focus-in

FZC : Looped in with the <u>first sinewave signal</u> ① DVD disc Lens sweep  $Up \rightarrow Down$

② CD disc Lens sweep Down  $\rightarrow$  Up

Note: Change the detecting edge direction

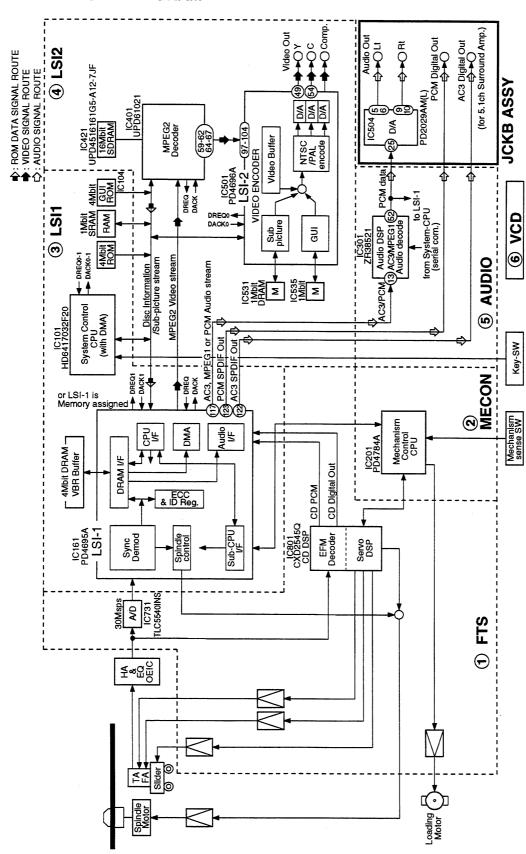

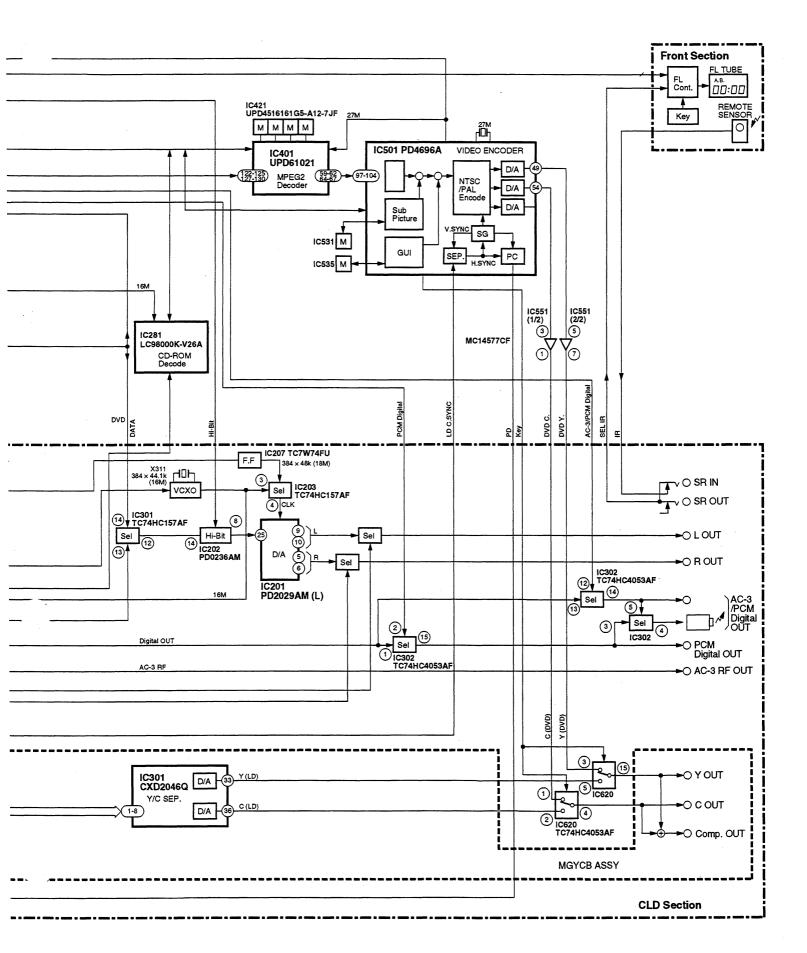

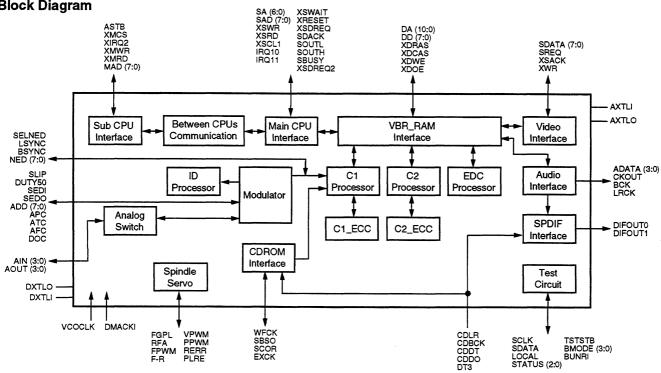

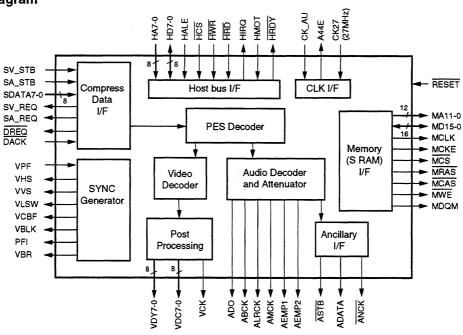

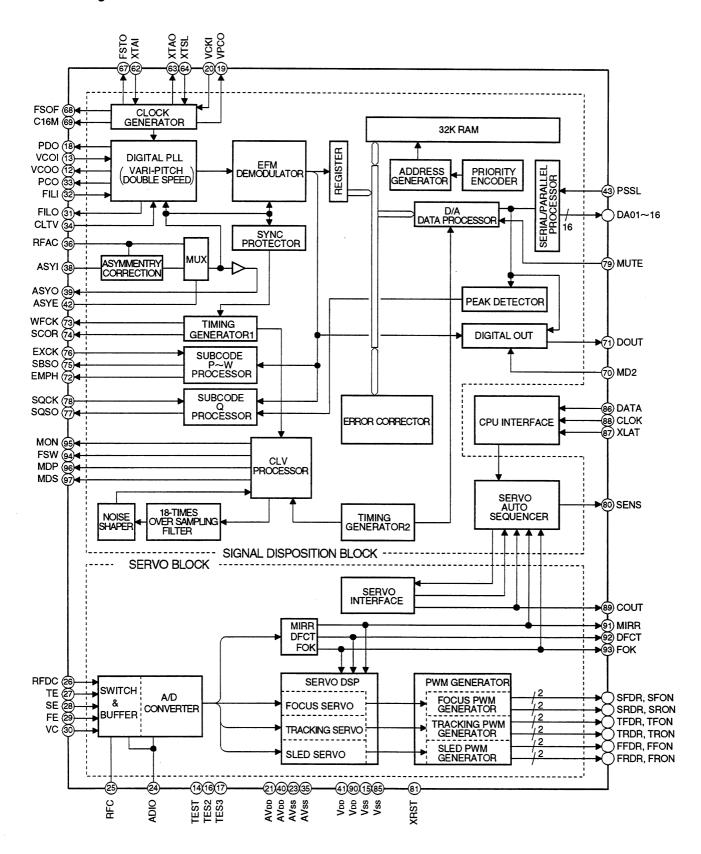

#### 3.2 DVL-90 AND DVL-700 3.2.1 OVERALL BLOCK DIAGRAM IC162 HM514800CJ-7 IC101 HD6417032F20 4M DRAM IC161 PD4695A System Control IC731 ③ DRAM I/F OEIC CPU I/F A/D TA FA TA FA SPDL Motor MPEG2 Video St vco DMA Slider Slider SPDL ECC AC-3/PCM S/P DIF OUT Cont. PCM S/P DIF OUT For CLD For DVD PCM Data Audio Sub-CPU Audio Stream 768 × 48k APC IC601 PA0065AM IC851 / BA6797FP IC801 CXD2545Q IC901 CXA2521AC EFM Decode IC301 ZR38521 52 IC201 PD4784A Digital Servo AC-3/MPEG1 Audio Decode DVD Mechanism Control OEIC Gain Ц∏H <sub>ЗЗМ</sub> 768 × 48k (36M) 16M [Š SI, SO, S SHAKE DVD TILT ERR Mecha SW IC101 PD0246A2 SLD DRV LOAD/TILT IC208 NJU6322KE SLD ERR LOAD/TILT DRV 768 × 48k (36M) LD Mechanism Control TURN DRV LD TILT ERR TURN MOTOR VCXO ERR TRKG IC901 LA9420M FOCS IC801 LA9425 Servo Control IC (ASP) IC802 LC78681KE LD DATA PSP DSP EFM Decode Sel Sub-Code IC352 CA0002AM Analog Audio Phillips Code LD C SYNC IC500 PD6159B IC101 PD3212A IC201 PDC016A A/D IC400 Memory Cont. (with DNR) Dual DVP LD-G (CD-G) LA7134M SPDL Cont VDEM IC102, IC103 MB81C1501PF IC202 LC32464P-80 VRAM Field Memory

#### 3.2.2 OPERATIONS

#### (1) Loading

In Compatible-Model mode, a command is serially transmitted from the DVD mechanism control computer to the CLD mechanism control computer. The CLD mechanism control computer controls the Loading Motor [Motor Driver IC803 (2/2)] with the PWM output from pin 24 (TILT OUT) while monitoring pins 33-35 (SW1, SW2, SW3).

#### (2) Slider Movement Toward the Inner Periphery

Once a disc is loaded, the DVD mechanism control computer orders the pickup to move to the disc-sensing position while monitoring pin 77 (SLDR POS). (The location of the disc-sensing position is decided by moving the pickup from the outer periphery to the inner periphery and again to the outer periphery to avoid sensing the turntable. In this case, the setting of the INSIDE SW is ignored.)

The subsequent operations are the same as those of the DV-500.

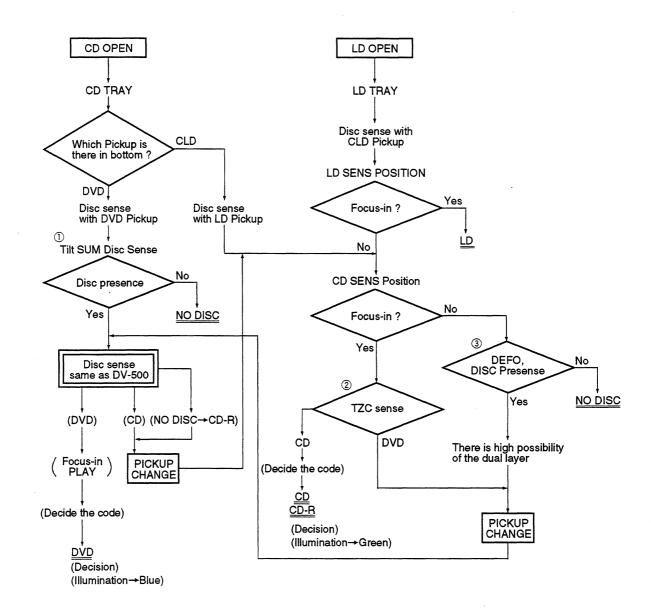

#### (3) Disc Sensing

Disc sensing is performed with the two pickups of the DVL-90 and DVL-700.

#### • CLD Pickup Side

A disc that is focused in at the LD sensing position is recognized as an LD.

When a disc is focused in at the CD sensing position, whether the disc is a DVD or CD is judged according to the TZC as follows:

After Focus-In, the disc is rotated, and its disc type is judged by the number of the TZC within a rotation at a specific rotation speed. The TZC is a signal in which a TE signal, via the LPF, comparator IC907 (1/2) and the switch (IC761), is input to pin 22 of the CLD mechanism control computer. If TZC  $\geq$  5, the disc is judged to be a CD, and if TZC<5, the disc is judged to be a DVD.

If focusing is not successful at the CD sensing position, the mechanism control computer, through pin 53, monitors pin 16 of the PSP (IC801) and judges whether a disc is loaded or not.

If the DEFO is kept at L for more than 2 ms during sweeping, it is judged that a disc is loaded, and the DVD pickup will be used. If the DEFO remains at H, it is judged that no disc is loaded

(Failure to focus in with a disc loaded is often caused by a dual-layered disc.)

#### • DVD Pickup Side

The DVL-90 and DVL-700 performs disc in/out sensing with the Tilt Sensor output and disc-type sensing by using the FE and sinewave signals. Sensing with the Tilt Sensor is required in addition to the DV-500 procedures to avoid judging as NO DISC when a sinewave signal is not detected with a CD-R disc. The method for judging DVD/CD is the same as with the DV-500, except for the following point: During the third sweep, in a case where the DV-500 would make a judgment of NO DISC, the DVL-90 and DVL-700 monitors pin 53 (Disc In/Out port) of the CLD mechanism control computer. If the port indicates that a disc is loaded, the DVL-90 and DVL-700 judges the disc as a CD-R and changes pickups.

#### (4) Disc-Size Sensing (8 cm/12 cm)

This procedure is not performed, because the DVD mechanism does not switch the spindle gain for 8 cm/12 cm.

#### (5) Differences from the DV-500

The following operations are added to correspond to CD-R discs and because the CLD pickup is added:

- ① Judgment of DISC IN/OUT with the DVD pickup tilt sum (because sinewave signal output is not reliable with CD-R discs)

- ② Judgment of DVD/CD according to the <u>TZC</u> signal during the CLD pickup operation

- ③ Judgment of DISC IN/OUT with the <u>DEFO</u> during the CLD pickup operation

# 4. TEST MODE

# 4.1 HOW TO ENTER/EXIT FROM TEST MODE

How to enter: To enter SD Test mode, press the ESC key

then the TEST key on the remote control unit. In SD Test mode, corresponding information will be displayed on the blue back screen. How to exit: Press the ESC key while in SD Test mode.

# **4.2 TEST MODE OPERATIONS**

| Command                                                                            | Condition                 | Key (Remote Control Unit) | Mode of the Remote Control Unit |

|------------------------------------------------------------------------------------|---------------------------|---------------------------|---------------------------------|

| Open                                                                               | STOP                      | REPEAT A                  | A8-48                           |

| Close                                                                              | OPEN                      | REPEAT A                  | A8-48                           |

| Stop                                                                               | PLAY                      | REPEAT B                  | A8-44                           |

| Play (startup the spindle)                                                         | STOP                      | TV/LDP                    | A8-0F                           |

| Pause (still picture)                                                              | PLAY                      | cx                        | A8-0E                           |

| Search address input (0- 9)                                                        |                           | 0~9                       | A8-00- 09                       |

| Search address input (A- F)                                                        | While entering an address | PGM+1 - 6                 |                                 |

| DSearch address crear                                                              | While entering an address | CLEAR                     | A8-45                           |

| ②Exit from Search input mode<br>①To enter Search address input mode                | Address = 0               |                           |                                 |

| ②Change of address input methods  (Absolute address→Addition→Subtraction)          |                           | +10                       | A8-1F                           |

| Search excution                                                                    |                           | CHAP/TIME                 | A8-13                           |

| racking open                                                                       | PLAY                      | STEP FWD                  | A8-54                           |

| racking close                                                                      | PLAY                      | STEP REV                  | A8-50                           |

| Slider in                                                                          | TR : Off                  | SCAN REV                  | A8-11                           |

| ow speed scan REV                                                                  | TR : On                   | Shuttle REV<br>SCAN REV   | A8-2C- 2F<br>A8-11              |

|                                                                                    |                           |                           |                                 |

| Scan REV (x4, x8, x16, x32)                                                        | TR : On                   | Shuttlr REV<br>SCAN FWD   | A8-2C- 2F<br>A8-10              |

| Slider out                                                                         | TR : Off                  | Shuttle FWD               | A8-28- 2B                       |

| ow speed scan FWD                                                                  | TR : On                   | SCAN FWD                  | A8-10                           |

| Scan FWD (x4, x8, x16, x32)                                                        | TR : On                   | Shuttle FWD               | A8-28- 2B                       |

| oading in                                                                          | STOP                      | SKIP REV                  | A8-53                           |

| oading out                                                                         | STOP                      | SKIP FWD                  | A8-52                           |

| ilt neutral                                                                        |                           | SPEED DOWN                | A8-46                           |

| ilt servo on                                                                       |                           | SPEED UP                  | A8-47                           |

| Filt servo off                                                                     | Tilt : On/N               | SKIP REV                  | A8-53                           |

|                                                                                    |                           | SKIP FWD                  | A8-52                           |

| Filt up                                                                            | PLAY                      | SKIP FWD                  | A8-52                           |

| Tilt down                                                                          | PLAY                      | SKIP REV                  | A8-53                           |

| _D on                                                                              |                           | TEST + 1                  | A8-5E + A8-01                   |

| Focus on                                                                           |                           | TEST + 2                  | A8-5E + A8-02                   |

| ocus sweep                                                                         |                           | TEST + 3                  | A8-5E + A8-03                   |

| ocus jump +                                                                        |                           | MULTI FWD                 | A8-58                           |

| Focus jump –                                                                       |                           | MULTI REV                 | A8-55                           |

| Гum B                                                                              | CLOSE                     | SIDE-B                    | A8-4E                           |

| 「urn A                                                                             | CLOSE                     | SIDE-A                    | A8-4D                           |

| Spindle auto servo                                                                 |                           | TEST + 4                  | A8-5E + A8-04                   |

| Spindle FG on                                                                      |                           | TEST + 5                  | A8-5E + A8-05                   |

| Spindle PLL on                                                                     |                           | TEST + 6                  | A8-5E + A8-06                   |

| AGC on                                                                             | AGC : Off                 | TEST + 7                  | A8-5E + A8-07                   |

| AGC off                                                                            | AGC : On                  | TEST + 7                  | A8-5E + A8-07                   |

| ATB on                                                                             | ATB : Off                 | TEST + 8                  | A8-5E + A8-08                   |

| ATB off                                                                            | ATB : On                  | TEST + 8                  | A8-5E + A8-08                   |

| ndication of the coefficient of CXD2545Q                                           |                           | TEST + 9                  | A8-5E + A8-09                   |

| D error rate indication                                                            | CD PLAY                   | TEST + 0                  | A8-5E + A8-00                   |

| Screen display on<br>Switching of Ver. and Rev. indications)                       | OSD : Off/On              | DISPLAY                   | A8-43                           |

| Screen display off                                                                 | OSD : On                  | AUDIO                     | A8-1E                           |

| Screen display on/off                                                              |                           | PROGRAM                   | A8-4C                           |

| Switching of ID display methodes<br>(decimal/hexadecimal)<br>Disc type designation |                           | DIG/ANA<br>HILITE/INTRO   | A8-0C                           |

| Disc type designation  Forced designation to DVD                                   |                           | +1                        | + A8-01                         |

| Forced designation to CD     Request for Disc sensing                              | STOP                      | +3+0                      | + A8-03<br>+ A8-00              |

| Tray close of disc sense inhibition                                                | Checker mode              | REPEAT A                  | A8-48                           |

#### 4.3 NOTES

- For measuring the DVD error rate, simultaneously press the ESC and PLAY keys while in the normal status.

The DVD error signal is then serially output from LSI-1 in sequence during playback.

- (2) Indications for the spindle status are as follows:

A/B : Spindle accelerator and brake

FG: FG servo

SRV: Rough, velocity/phase servo

O\_S : Offset addition, rough, velocity/phase servo

- (3) There are three methods for entering a search address:

- ① Absolute address designation

→Searching for the address entered

(indication for the most significant digit : >)

- 2 Additional input

- →Searching for the address with the current ID number plus an entered number

(indication for the most significant digit: +)

- ③ Subtractive input

- →Searching for the address with the current ID number minus an entered number

(indication for the most significant digit : -) The above modes can be changed by pressing the +10 key.

Note: A number for addition or subtraction must be

entered in hexadecimal.

- (4) If you turn the power on while short-circuiting the short-circuit terminal at the side of the system control computer, the unit will forcibly enter Test mode. If the FL control computer is set to Checker mode, disc sensing will not be started, even if a disc is loaded. Disc sensing will also not be performed if the tray is opened/closed by your pressing REPEAT A key while in Checker mode. However, disc sensing will be started if the OPEN/CLOSE key on the main unit or on the remote control unit is pressed.

- (5) If disc-type designation is forcibly executed during a mode other than Checker mode, the system control computer will abandon disc-type designation after setting the mechanism control computer. Therefore, after startup of the unit, disc sensing will be performed again for safety. If disc-type designation is forcibly executed during Checker mode, as disc-type designation is not abandoned, playback will be immediately started.

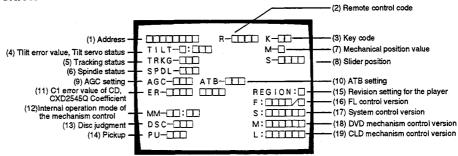

#### 4.4 TEST MODE DISPLAY SPECIFICATIONS

Consecutive single-OSD display is supported during Test mode. The screen is composed 10 lines with a maximum of 24 characters per line. Simultaneous use of RAM Display mode or Debug Display mode cannot be performed.

#### 4.4.1 Screen Composition

# DV-500, DVL-90, DVL-700

#### 4.4.2 Description of Each Item on the Display

(1) Address indication

The address being traced is displayed in number:

DVD : ID indication [\* \* \* \* \* \* \* \*]

(hexadecimal number, 8 digits)

CD/LD (CLV) : A-TIME (min. sec.) [0000 \*\*\*\*]

LD (CAV) : FRAME [000 \*\*\*\*\*]

(Note: For DVDs, decimal-number indication is

possible.)

- (2) Key code indication for the remote control unit [R-\*\*\*] The code for the key pressed on the remote control unit, which is received by the FL control computer, is displayed while the key is pressed. In the case of the double code, the second code will be displayed.

- (3) Key code indication for the main unit [K-\*\*]

The code for the key pressed on the main unit, which is received by the system control computer, is displayed while the key is pressed.

- (4) Tilt error value, Tilt servo status [TILT-\*:\*\*\*]

Tilt error value : [0]-[F]

Tilt servo status: Tilt neutral [N]

Tilt servo on [ON]

Tilt servo off [OFF]

(5) Tracking status [TRKG-\*\*\*]

Tracking on : [ON]

Tracking off : [OFF]

(6) Spindle status [SPDL-\*\*\*]

Spindle accelerator and brake : [A/B]

FG servo : [FG]

Rough, velocity/phase servo : [SRV]

Offset addition, rough, velocity/phase servo : [O\_S]

(7) Mechanism position value [M-\*]

Position code: [0]-[8]

(8) Slider Position [S-\*\*\*\*]

CD TOC area : [IN]

CD active area : [CD]

CDV video area : [CDV]

LD active area : [LD]

Side B inside : [B IN]

(9) AGC setting [AGC-\*\*]

AGC on : [ON] AGC off : [OFF]

(10)ATB setting [ATB-\*\*]

ATB on : [ON] ATB off : [OFF] (11)Indications for the following two types of information can be switched:

① C1 error value of CDs [ER-C1\*\*\*\*]

C1 error value of CDs (up to four digits)

(Note: Error value indication for DVDs cannot be used.)

② Q coefficient for CXD2545Q [KS-[\*\*]\*\*\*\*]

The address for the designated coefficient (2 digits) and its setting number (4 digits) are displayed.

(12)Internal operation mode for the mechanism control computer [MM-\*\*: \*\*]

Internal mechanism mode (2 digits) and internal mechanical step (2 digits) of the mechanism control

(Note: For details, see the specifications of the mechanism control computer.)

(13)Disc sensing

computer

The type of discs loaded is displayed : [DVD], [CD], [CDV], [LD], [VCD], []

12- -- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (---- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (--- 17 (---- 17 (---- 17 (---- 17 (---- 17 (---- 17 (---- 17 (---------17 (

(14)Pickup (PU-\*\*\*]

The pickup being operating is displayed:

DVDs: [DVD] CLDs: [CLD]

(15) Revision setting for the player [REGION: \*]

Setting numbers: [1]-[8]

(16) Version of the FL control computer

Destination setting : [F:\*\*\*\*/\*]

Four characters in front represent the type of model:

Base : Base model

Omni : Compatible model

B/FX: Base FX

O\_KR: Compatible Karaoke

B\_OM: Base OEM

O\_OM: Compatible OEM

Two characters that follow represent the destination code:

J:/J, U:/KU, C:/KC, S:SL, W:WY,

K: KU/KC, E: Elite

Version No.: [F:\*.\*]

(17) Version of the system control computer

Parts number (PD\*\*\*\*) : [S:\*\*\*\*]

Version No. : [S:\*.\*\*]

(18) Version of the DVD mechanism control computer

Parts number (PD\*\*\*\*\*) : [M:\*\*\*\*\*]

Revision No. : [M:\*\*\*\*\*]

(19) Version of the CLD mechanism control computer

Parts number (PD\*\*\*\*\*) : [L:\*\*\*\*\*]

Revision No. : [L:\*.\*\*\*]

# 5. IC INFORMATION

• The information in the list is basic information and may not correspond exactly to that shown in the schematic diagrams.

#### List of IC

PD4753B

HM514800CJ-7

UPD4516161G5-A12-7JF

BA6797FP

PD0246A2

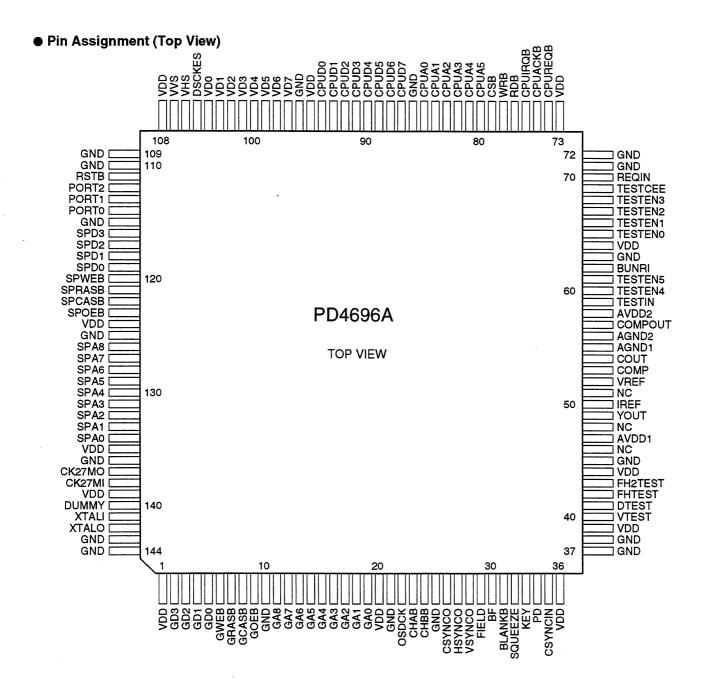

PD4784A ZR38521 PD4696A

CXA2521AQ

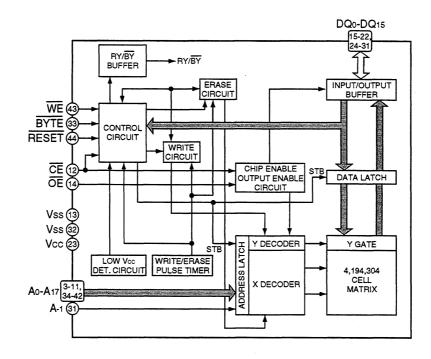

MBM29F400TA-70PF

PD0236AM HD6417032F20

UPD61021

PA0065AM TLC5540INS

PD4695A

IR3C07N

CXD2545Q

■ PD4753B [DV-500 : (FLKB ASSY : IC101)]

[DVL-90, DVL-700: (FLPB ASSY: IC101)]

• MODE CONTROL IC

| No. | Name  | Function Name    | 1/0 | Function                                                | ACTIVE                    |

|-----|-------|------------------|-----|---------------------------------------------------------|---------------------------|

| 1   | P94   | T6               | 0   |                                                         |                           |

| 2   | P93   | T5               | 0   |                                                         |                           |

| 3   | P92   | T4               | 0   |                                                         |                           |

| 4   | P91   | Т3               | 0   | FL timing output.                                       | H : ON                    |

| 5   | P90   | T2               | 0   |                                                         |                           |

| 6   | P81   | T1               | 0   |                                                         |                           |

| 7   | P80   | ТО               | 0   |                                                         |                           |

| 8   | VDD   | Vcc              | _   | -                                                       | <b> </b> -                |

| 9   | P27   | Angle LED        | 0   | Angle LED ON/QFF.                                       | H:ON                      |

| 10  | P26   | SIDE A LED       | 0   | SIDE A LED ON/OFF. Basically (NC) only with compatible. | H:ON                      |

| 11  | P25   | SIDE B LED       | 0   | SIDE B LED ON/OFF. Basically (NC) only with compatible. | H:ON                      |

| 12  | P24   | DVD illumination | 0   | DVD illumination lamp ON/OFF.                           | H:ON                      |

| 13  | P23   | XRDY             | 0   | Communications handshake line with system controller.   | L: communications enabled |

| 14  | P22   | SCK1             | 1/0 | Communication clock output with system controller.      | -                         |

| 15  | P21   | SO1              | 1/0 | Communication data output with system controller.       | -                         |

| 16  | P20   | SI1              | 1   | Communication data input with system controller.        | -                         |

| 17  | RESET | RESET IN         | 1   | Reset input.                                            | L: reset                  |

| 18  | P74   | Condition LED    | 0   | Condition OED ON/OFF.                                   | L:ON                      |

| 19  | P73   | Last memory LED  | 0   | Last memory LED ON/OFF.                                 | L:ON                      |

| 20  | AVss  | Vss              | -   | -                                                       | _                         |

| 21  | P17   | POWER ON         | 0   | SW5V ON/OFF.                                            | H:ON                      |

| 22  | P16   | RESET OUT        | 0   | System reset output.                                    | L: reset                  |

| 23  | P15   | (NC)             | 0   | -                                                       | -                         |

| 24  | P14   | (NC)             | 0   | -                                                       | -                         |

| 25  | P13   | KIN1             | 1   | Key input.                                              |                           |

| 26  | P12   | KINO             | ı   | Key input.                                              |                           |

| 27  | P11   | MS1              | I   | Destination determination input.                        |                           |

| 28  | P10   | MS0              |     | Destination determination input.                        |                           |

| 29  | AVDD  | AVDD             | -   | -                                                       | _                         |

| 30  | AVREF | AVREF            |     | -                                                       | -                         |

| No. Name | Function Name | I/O                   | Function                                                                            | ACTIVE                    |

|----------|---------------|-----------------------|-------------------------------------------------------------------------------------|---------------------------|

| 31 P04   | P04           | 1                     | (Not used)                                                                          | -                         |

| 32 XT2   | (NC)          | _                     |                                                                                     |                           |

|          | Vss           | ı                     |                                                                                     | _                         |

|          | X1            | 1                     | Microprocessor clock connection.                                                    |                           |

|          | X2            | _                     | Microprocessor clock connection.                                                    |                           |

|          | (NC)          | 0                     |                                                                                     |                           |

|          | (NC)          | 0                     |                                                                                     |                           |

|          | (NC)          | 0                     | -                                                                                   | _                         |

|          | (NC)          | 0                     |                                                                                     |                           |

|          | (NC)          | <del>-</del>          |                                                                                     |                           |

|          |               | $\frac{\circ}{\circ}$ |                                                                                     |                           |

|          | (NC)<br>LT1   |                       | Communications handshake line with eveters as the line                              | l . communications        |

|          | SEL IR        | <u> </u>              | Communications handshake line with system controller.  Remote control signal input. | L: communications enabled |

|          | SEL IR<br>IC  |                       |                                                                                     |                           |

|          |               |                       | -                                                                                   | -                         |

|          | (NC)          | 0                     |                                                                                     |                           |

|          | (NC)          | 0                     | <del>-</del>                                                                        | -                         |

|          | (NC)          | 0                     |                                                                                     |                           |

|          | VDD           |                       | -                                                                                   | -                         |

|          | DISP LED      | 0                     | Display LED ON/OFF.                                                                 | H:ON                      |

|          | GUI LED       | 0                     | GUI LED ON/OFF.                                                                     | H:ON                      |

|          | (NC)          | 0                     |                                                                                     |                           |

|          | (NC)          | 0                     | <del> -</del>                                                                       | -                         |

|          | (NC)          | 0                     |                                                                                     |                           |

|          | S15           | 0                     |                                                                                     |                           |

|          | S14           | 0                     |                                                                                     |                           |

|          | S13           | 0                     | FL segment output.                                                                  | H:ON                      |

|          | S12           | 0                     | TE segment output                                                                   | 11.014                    |

| 62 P116  | S11           | 0                     |                                                                                     |                           |

|          | S10           | 0                     |                                                                                     |                           |

| 64 P114  | (NC)          | 0                     |                                                                                     | _                         |

| 65 P113  | (NC)          | 0                     |                                                                                     |                           |

| 66 P112  | S9            | 0                     |                                                                                     |                           |

| 67 P111  | S8            | 0                     |                                                                                     |                           |

| 68 P110  | S7            | 0                     | FL segment output.                                                                  | H:ON                      |

| 69 P107  | S6            | 0                     |                                                                                     |                           |

| 70 P106  | S5            | 0                     |                                                                                     |                           |

|          | -30V          | _                     | Input for -30V.                                                                     |                           |

|          | S4            | 0                     |                                                                                     |                           |

|          | S3            | 0                     |                                                                                     |                           |

|          | S2            | 0                     | FL segment output.                                                                  | H:ON                      |

|          | S1            | 0                     | · ·                                                                                 |                           |

|          | S0            | 0                     |                                                                                     |                           |

|          | T10           | 0                     |                                                                                     |                           |

|          | T9            | 0                     |                                                                                     |                           |

|          | T8            | 0                     | FL segment output.                                                                  | H:ON                      |

|          |               |                       |                                                                                     |                           |

|          | T7            | 0                     |                                                                                     |                           |

# **■ PD0246A2 (CLD MAIN ASSY : IC101)(DVL-90, DVL-700 ONLY)**

• LD MECHANISM CONTROL IC

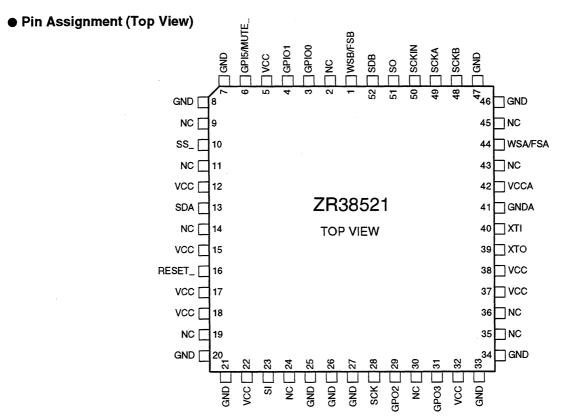

# ● Pin Arrangement (Top View)

|                      |            |                          |                 |    | 1            |         |

|----------------------|------------|--------------------------|-----------------|----|--------------|---------|

| +5V ·                | _          | l Vcc                    | P20/I/O         | 64 | XANA         | (O,H)   |

| RWC (O,L)            |            | P67/O                    | P21/I/O         | 63 | — xcx        | (O,L)   |

| XPLAY (O,H)          |            | B P66/O                  | P22/I/O         | 62 | SQ2          | (O,H)   |

| SCK3/XCQCK (O,H)     |            | P65/ O                   | P23/I/O         | 61 | SQ1          | (O,H)   |

| XCD (O,H)            | -          | P64/ O                   | P24/I/O         | 60 | — SRDMUTE    | (O,H)   |

| TILTERR (A/D)        | <b>—</b> l | P63/A/D 3                | P25/I/O         | 59 | — WRQ        | (1)     |

| TBALERR (A/D) -      |            | P62/A/D 2                | P26/I/O         | 58 | XFOK         | (1)     |

| SLDRERR (A/D)        | -          | B P61/A/D 1              | P27/I/O         | 57 | - DETPOW     | (1)     |

| SLDRPOS (A/D) -      |            | P60/A/D 0                | P00/I/O         | 56 | - XCLD_P.U_0 | OUT (1) |

| FSEQ (1) ·           |            | 0 P47/I/O/INT4           | P01/I/O         | 55 | - XTURNA     | (1)     |

| CURRENT DET (1)      | _          | 1 P46/I/O/INT3           | P02/I/O         | 54 | — XTURNB     | (1)     |

| TBALDRV (PWM,L)      |            | 12 P45/I/O/PWM2          | P03/I/O         | 53 | TILT SUM/DEF | ECT (I) |

| SHAKE (I/O,Z)        |            | 3 P44/I/O/DOCI           | P04/I/O         | 52 | - NROFF      | (O,L)   |

| RFCORR (O,L)         |            | 4 P43/I/O/MACS           | P05/I/O         | 51 | N.C.         | (O,L)   |

| SQOUT (I)            |            | 15 P42/I/O/SI2           | P06/I/O         | 50 | - DOCINH     | (1)     |

| COIN/SO3 (O,H) -     | -          | 6 P41/I/O/SO2            | P07/I/O         | 49 | — TZC SEL    | (O,H)   |

| CQCK/SCK3 (O,H)      |            | 7 P40/I/O/SCK2           | P10/I/O         | 48 | DVPLAT       | (O,H)   |

| SLDRDRV (PWM,Z)      | _          | 18 P37/I/OPWM 1          | P11/I/O         | 47 | — THOLD      | (1)     |

| SI1 (I) -            | -1         | 19 P36/I/O/SI1           | P12/I/O         | 46 | — N.C.       | (O,L)   |

| SO1 (O,H)            | <b>—</b> i | 20 P35/I/O/SO1           | P13/I/O         | 45 | — N.C.       | (O,L)   |

| SCK1 (I/O) -         | -          | 21 P34/I/O/SCK1          | P14/I/O         | 44 | N.C.         | (O,L)   |

| TZC (1) -            |            | 22 P33/I/O/ <u>CNT</u> R | P15/I/O         | 43 | — MEMLAT     | (O,H)   |

| SBSY (I)             |            | 23 P32/I/O/INT2          | P16/I/O         | 42 | — WFM/VLOCK  | (1)     |

| TILTDRV (I/O,Z)      |            | 24 P31/I/O               | <u>P17/l/</u> O | 41 | — D_EXT      | (O,L)   |

| TURNDRV (3 STATE,I). | <b>—</b>   | 25 P30/ <u>I/O</u>       | Vsync/I         | 40 | XPBV         | (1)     |

| XPBV (1)             | -1         | 26 P50/INT1              | Hsync/I         | 39 | XPBH         | (1)     |

| CNVSS -              | -          | 7 CNVss                  | DATA/I          | 38 | DATA         | (1)     |

| XRESET .             |            | 8 RESET                  | P53/I           | 37 | — FG         | (1)     |

| XIN -                |            | 29 Xin                   | P54/I           | 36 | — TBCLOCK    | (1)     |

| XOUT .               |            | 30 Xou                   | P55/I           | 35 | SW2          | (1)     |

| Φ .                  |            | 31 Ф                     | P56/I           | 34 | — SW3        | (1)     |

| GND -                | [          | 32 Vss                   | P57/I           | 33 | — SW1        | (1)     |

|                      | L          |                          |                 |    |              |         |

| No. | Pin Name   | 1/0   | Pin Function                                                                                                                                           |

|-----|------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | vcc        | -     | Power supply pin Apply 5V ± 10%                                                                                                                        |

| 2   | RWC        | 0     | DSP read/write command signal output "L"= Read "H"= Write                                                                                              |

| 3   | XPLAY      | 0     | Signal output during spindle servo "L"= During servo "H"= During acceleration, brake and stop                                                          |

| 4   | sскз/хсоск | 0     | DVP/DSP clock switch "H"= DVP "L"= DSP                                                                                                                 |

| 5   | XCD        | 0     | LD/CD switch signal output "L= CD "H"= LD                                                                                                              |

| 6   | TILTERR    | I A/D | This signal is A/D converted as the tilt servo control input. Control the tilt motor so that this signal becomes 2.5V.                                 |

| 7   | TBALERR    | I A/D | Tracking balance error signal input This signal is A/D converted as the tracking offset control input.                                                 |

| 8   | SLDERR     | 1 A/D | This signal is A/D converted as the slider servo control input. Control the slider motor so that this signal becomes 2.5V.                             |

| 9   | SLDPOS     | l A/D | Pickup position detection switch input Detect the position by reading A/D input value which each switches are resistance divided.                      |

| 10  | FSEQ       | 1     | Subcode sync. confirmity detection signal input "L"= Not confirmity "H"= Confirmity                                                                    |

| 11  | CURRENTDET | l     | Spindle over-current detection signal input "L" = Over current "H"= Normal                                                                             |

| 12  | TBALDRV    | O PWM | Output the tracking offset signal to PWM output, then use for auto tracking offset. 910µsec period, tri-state control H, L, Z                          |

| 13  | SHAKE      | 1/0   | Handshake signal for data communication with the mode control IC This pin is the bilateral data line and each microprocessor control the Input/Output. |

| 14  | RFCORR     | 0     | RF correction switch signal output "H"= Gain UP CD, CDV-A:Low, CAV inner circuit gain up, others are High.                                             |

| 15  | SQOUT      | 1     | Command data input from DSP Read out SUBQ                                                                                                              |

| 16  | SO3/COIN   | 0     | Command data output to DVP/DSP                                                                                                                         |

| 17  | SCK3/CQCK  | 0     | DVP/DSP read/write command clock output Read-in at rising edge                                                                                         |

| 18  | SLDDRV     | O PWM | Slider control signal output 5V= FWD, 0V= REV, 2.5V= STOP 910µsec period, tri-state control H, L, Z                                                    |

| No. | Pin Name | I/O                                              | PIn Function                                                                                                           |  |  |  |  |  |  |

|-----|----------|--------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 19  | SI1      | ı                                                | Data input from the mode control IC                                                                                    |  |  |  |  |  |  |

| 20  | SO1      | 0                                                | Serial data output to the mode control IC                                                                              |  |  |  |  |  |  |

| 21  | SCK1     | 1/0                                              | lock for serial communication with the mode control IC ecomes input mode without communicate with the mode control IC  |  |  |  |  |  |  |

| 22  | TZC      | I INT                                            | acking error zero cross signal input onitor this signal when searching track count in the miss clamp detection         |  |  |  |  |  |  |

| 23  | SBSY     | ١                                                | Subcode block sync. input                                                                                              |  |  |  |  |  |  |

| 24  | TILTDRV  | 1/0                                              | LOAD/TILT control output  0.5V= Tray IN, OUT/Tilt DOWN, UP 2.5V=STOP Use for tilt servo that tilt drive is PWM output. |  |  |  |  |  |  |

| 25  | TURNDRV  | 0                                                | Turn drive signal output                                                                                               |  |  |  |  |  |  |

| 26  | XPBV     | 1                                                | Playback vertical sync. signal input of LD/CDV "L"= During vertical sync.                                              |  |  |  |  |  |  |

| 27  | CNVSS    | i                                                | Ground for A/D conversion                                                                                              |  |  |  |  |  |  |

| 28  | XRESET   | Ī                                                | Reset signal input "L"= Reset "H"= Release reset Mode control IC is controlled.                                        |  |  |  |  |  |  |

| 29  | XIN      | l                                                | 9MHz clock oscillation input                                                                                           |  |  |  |  |  |  |

| 30  | XOUT     | 0                                                | 9MHz clock oscillation output                                                                                          |  |  |  |  |  |  |

| 31  | N.C.     | 0                                                | Not used                                                                                                               |  |  |  |  |  |  |

| 32  | GND      |                                                  | Ground                                                                                                                 |  |  |  |  |  |  |

|     | SW1      | ·····                                            |                                                                                                                        |  |  |  |  |  |  |

|     | SW3      | i                                                | Switch input for Loading/Tilt position detection                                                                       |  |  |  |  |  |  |

|     | SW2      | •                                                | which input for Educating, file position detection                                                                     |  |  |  |  |  |  |

|     | TBCLOCK  |                                                  | Spindle lock signal input "L"= Unlock "H"= Lock                                                                        |  |  |  |  |  |  |

|     |          | <u> </u>                                         |                                                                                                                        |  |  |  |  |  |  |

|     | FG       | <u> </u>                                         | Spindle motor FG signal input 16 outputs per rotation Used after dividing by 2 in the microprocessor                   |  |  |  |  |  |  |

| 38  | DATA     | !                                                | Input for Phillips code decoder with built-in mechanism controller                                                     |  |  |  |  |  |  |

|     | XPBH     |                                                  | Playback H-SYNC input for Phillips code decoder                                                                        |  |  |  |  |  |  |

|     | XPBV     | <u> </u>                                         | Playback V-SYNC input for Phillips code decoder                                                                        |  |  |  |  |  |  |

|     | D_EXT    | 0                                                | Control signal output for video dynamic extension "H"= ON "L"= OFF                                                     |  |  |  |  |  |  |

| 42  | WFM      | <u> </u>                                         | Field discrimination signal from DVP "H"= ODD "L"= EVEN                                                                |  |  |  |  |  |  |

| 43  | MEMLAT   | 0                                                | Serial control latch output of memory control IC PD3212A Latches at falling edge.                                      |  |  |  |  |  |  |

| 44  | N.C.     | 0                                                | Not used                                                                                                               |  |  |  |  |  |  |

| 45  | N.C.     | 0                                                | Not used                                                                                                               |  |  |  |  |  |  |

| 46  | N.C.     | 0                                                | Not used                                                                                                               |  |  |  |  |  |  |

| 47  | THOLD    | 1                                                | Track jump accelerating / decelerating signal input "L"= Other "H"= During accelerating / decelerating                 |  |  |  |  |  |  |

| 48  | DVPLAT   | 0                                                | PD6159B serial latch signal output Latches at falling edge.                                                            |  |  |  |  |  |  |

| 49  | TZCSEL   | 0                                                | TZC switch signal output "H"= at normal "L"= at CD/DVD disc discrimination                                             |  |  |  |  |  |  |

| 50  | DOCINH   | 0                                                | Control the clamp pulse and clamp killer by tri-state value                                                            |  |  |  |  |  |  |

| 51  | N.C.     | 0                                                | Not used                                                                                                               |  |  |  |  |  |  |

| 52  | NROFF    | 0                                                | Noise reduction control output by VDEM "L"= Normal "H"= Not NR                                                         |  |  |  |  |  |  |

|     | TILT SUM | 0                                                | Disc present/absent detecting signal input by the tilt sum in the DVD P.U. mode "H"= Absent "L"= Present               |  |  |  |  |  |  |

| 54  | XTURNB   | ī                                                | Turn switch input "H"= Side A / turn "L"= Side B                                                                       |  |  |  |  |  |  |

| 55  | XTURNA   |                                                  | Turn switch input "H"= Side B / turn "L"= Side A                                                                       |  |  |  |  |  |  |

| 56  | XLDPUCUT | <del>-                                    </del> | LD P.U. out position detecting switch input "H"= LD P.U. active "L"= LD P.U. out position                              |  |  |  |  |  |  |

| 57  | DETPOW   | 1                                                | Use for power abnormal signal input port "L"= Normal "H"= Abnormal                                                     |  |  |  |  |  |  |

| 58  | XFOK     | · ·                                              | Focus servo lock signal input "L"= Lock "H"= Unlock Use for lock detection of focus servo                              |  |  |  |  |  |  |

|     | WRQ      | 1                                                | Subcode Q reading OK signal input "L"= NG "H"= OK This pin will be H when subcode Q data passed by CRC check.          |  |  |  |  |  |  |

| 60  | SRDMUTE  | 0                                                | Mute control signal output for AC3 Release MUTE during playback. "L"= Release MUTE "H"= MUTE                           |  |  |  |  |  |  |

|     | SQ1      | 0                                                | Analog audio switching signal output 1/L "L"= Squelch OFF "H"= Squelch ON                                              |  |  |  |  |  |  |

|     | SQ2      | 0                                                | Analog audio switching signal output 2/R "L"= Squelch OFF "H"= Squelch ON                                              |  |  |  |  |  |  |

|     | XCX      | 0                                                | Analog audio CX noise reduction switching signal output "L"= CX ON "H"= CX OFF                                         |  |  |  |  |  |  |

|     | <u> </u> |                                                  | Digital / Analog audio switching signal output "L"= Analog "H"= Digital                                                |  |  |  |  |  |  |

| 64  | XANA     | 0                                                | Digital / Arialog audio switching signal output L = Arialog H = Digital                                                |  |  |  |  |  |  |

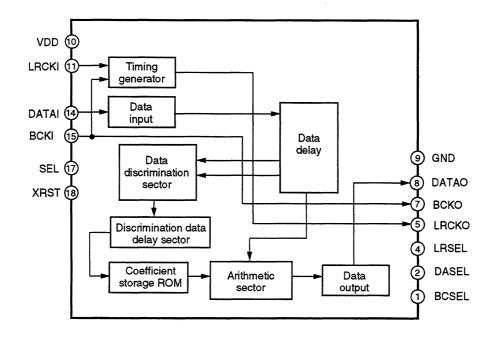

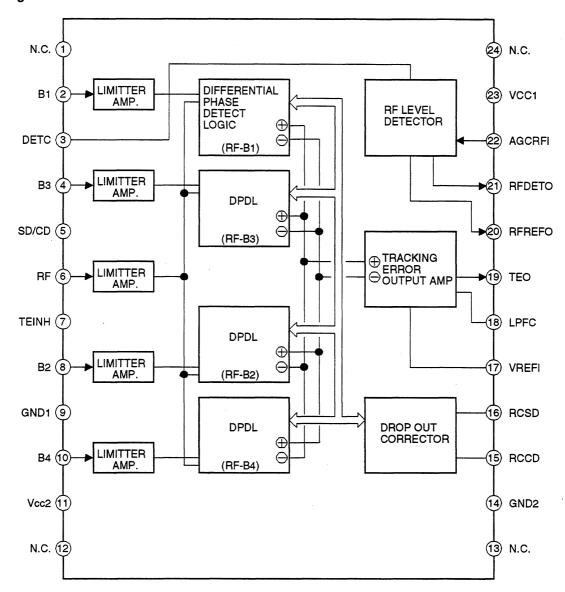

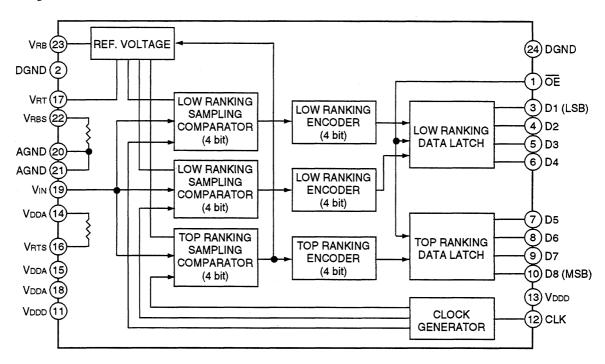

■ PD0236AM [DV-500 : (AUDB ASSY : IC102)]

[DVL-90, DVL-700 : (CLD MAIN ASSY : IC202)]

• HI-BIT IC

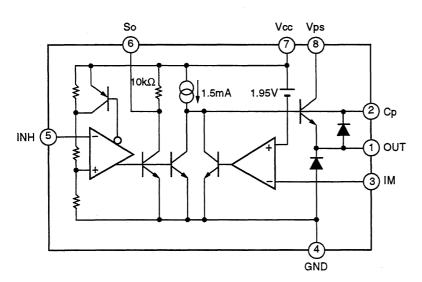

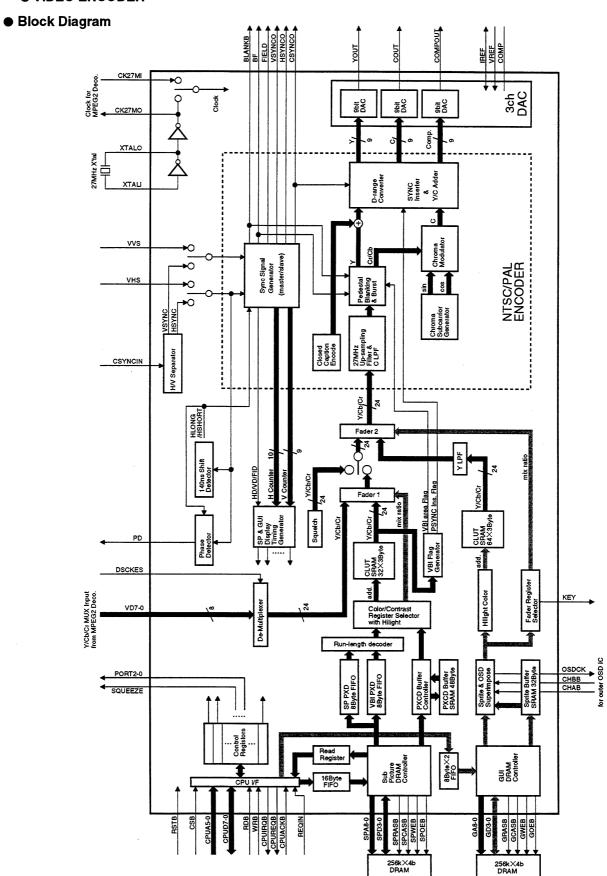

#### Block Diagram

| No. | Pin Name | I/O | Pin Function                                                                                                                                               |

|-----|----------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | BCSEL    | lp  | fs selection of bit clock (built-in pull-up) H: BCKI = 48fs , L: BCKI = 64fs                                                                               |